Model Checking the HAVi Leader Election Protocol

J.M.T. Romijn

Software Engineering (SEN)

SEN-R9915 June 30, 1999

Report SEN-R9915 ISSN 1386-369X

CWI P.O. Box 94079 1090 GB Amsterdam The Netherlands

CWI is the National Research Institute for Mathematics and Computer Science. CWI is part of the Stichting Mathematisch Centrum (SMC), the Dutch foundation for promotion of mathematics and computer science and their applications.

SMC is sponsored by the Netherlands Organization for Scientific Research (NWO). CWI is a member of ERCIM, the European Research Consortium for Informatics and Mathematics.

Copyright © Stichting Mathematisch Centrum P.O. Box 94079, 1090 GB Amsterdam (NL) Kruislaan 413, 1098 SJ Amsterdam (NL) Telephone +31 20 592 9333 Telefax +31 20 592 4199

## Model Checking the HAVi Leader Election Protocol

Judi Romijn

CWI

P.O. Box 94079, 1090 GB Amsterdam, The Netherlands

judi@cwi.nl

#### **ABSTRACT**

The HAVi specification [9] proposes an architecture for audio/video interoperability in home networks. Part of the HAVi specification is a distributed leader election protocol. We have modelled this leader election protocol in Promela and Lotos and have checked several properties with the tools Spin and Xtl (from the Cæsar/Aldébaran package).

It turns out that the protocol does not meet some safety properties and that there are situations in which the protocol may never converge to designate a leader. Our conclusion is that realistic timing requirements on sending and processing of messages should be added to the HAVi specification. Then a (timed) formal verification could give a definite answer with respect to correctness of the leader election protocol.

1991 Mathematics Subject Classification: 68M10, 68Q10, 68Q22, 68Q45, 68Q60, 68Q65 1991 ACM Computing Classification System: C.2.2, D.2.4, D.3.3, F.1.1, F.1.2, F.4.1, G.4

Keywords and Phrases: model checking, protocol verification, abstraction, process algebra, temporal logic, safety, liveness

*Note:* This research was carried out as part of the project "Specification, Testing and Verification of Software for Technical Applications" at the Stichting Mathematisch Centrum for Philips Research Laboratories under Contract RWC-061-PS-950006-ps.

# Table of Contents

| 1            | Introduction                                                                                                                                                                                                                                                                                                                                                                                      | 3                                      |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2            | The DCM Manager leader election protocol 2.1 Protocol                                                                                                                                                                                                                                                                                                                                             | <b>4</b><br>4<br>5                     |

| 3            | Languages and tools3.1 Spin and Promela3.2 Lotos, Cæsar/Aldébaran and Xtl                                                                                                                                                                                                                                                                                                                         | <b>5</b><br>6                          |

| 4            | Modelling decisions4.1 General description4.2 Promela4.3 Lotos                                                                                                                                                                                                                                                                                                                                    | 7<br>7<br>9<br>11                      |

| 5            | Model checking experiments  5.1 Safety: At most one leader  5.2 Safety: Best candidate becomes final leader  5.3 Safety: All agree on the final leader  5.4 Liveness: Eventually there will always be a final leader  5.5 Is the HAVi protocol wrong?  5.6 Statistics                                                                                                                             | 12<br>14<br>15<br>16<br>19<br>21<br>22 |

| 6            | Conclusions 6.1 Concerning Spin 6.2 Concerning Cæsar/Aldébaran and Lotos 6.3 Comparison of the tools 6.4 Concerning this experiment                                                                                                                                                                                                                                                               | 24<br>24<br>26<br>26<br>28             |

| Re           | eferences                                                                                                                                                                                                                                                                                                                                                                                         | 28                                     |

| A            | Excerpts from the HAVi Specification                                                                                                                                                                                                                                                                                                                                                              | 34                                     |

| В            | Excerpts from the IEEE 1394 Standard                                                                                                                                                                                                                                                                                                                                                              | 41                                     |

| $\mathbf{C}$ | The input files for Spin  C.1 Promela model for 3 DCM Managers with asynchronous communication (final leader)  C.2 Promela model for 3 DCM Managers with asynchronous communication (leader)  C.3 Promela model for 3 DCM Managers with asynchronous communication (end states) .  C.4 Promela model for 3 DCM Managers with synchronous communication  C.5 Promela assertions for 3 DCM Managers | 43<br>43<br>50<br>51<br>53<br>53       |

| D            | The input files for Cæsar/Aldébaran and Xtl  D.1 ACT-ONE naturals library for 3 DCM Managers                                                                                                                                                                                                                                                                                                      | 55<br>56<br>61<br>69<br>76<br>84       |

1. Introduction 3

## 1 Introduction

The Home Audio/Video Interoperability (HAVi) project [9] is a joint effort by eight consumer electronics companies to solve interoperability problems for audio/video networks in the home environment.

The HAVi specification specifies a set of Application Programming Interfaces (APIs) and protocols that allow consumer electronics manufacturers and third parties to develop applications for the home network. Thus the home network is viewed as a distributed computing platform, and the primary goal of the HAVi architecture is to assure that products from different vendors can cooperate to perform application tasks. The HAVi architecture is supposed to work on top of an IEEE 1394 serial bus [16, 17].

There are two types of HAVi devices: controllers and controlled devices. The controller acts a host for controlled devices via a Device Control Module (DCM). Installation and allocation of such DCMs is done by a HAVi software element which is called the Device Control Module Manager (DCM Manager). Each controller is supposed to have a DCM Manager. All DCM Managers have to cooperate with each other to ensure that the installation and allocation of DCMs works properly. A complicating factor here is the dynamic plug-and-play character of the 1394 network. Each time when a change in the 1394 network occurs, the DCM Managers restart their activities by first choosing a leader among them, and then under the control of the designated leader, complete their DCM controlling tasks.

The purpose of the leader election is that the DCM Manager with the best capabilities will play a central role in the DCM controlling tasks. Since not all of these capabilities are persistent and globally available, the DCM Managers need to communicate to find out which one is the best candidate for leadership.

In this paper, we study the leader election protocol between the DCM Managers. Our goal is to analyse this protocol with several model checking tools, to determine whether the protocol is correct, and to compare the model checking tools. Our approach is to construct a model of the behaviour of the protocol in a suitable formal language, and to establish certain properties through model checking. Model checking is a verification approach where one checks whether a property holds by exploring the reachable state space of the model. The manual construction of such proofs is a tedious and error-prone process. Nowadays, there are several tools that fully automate the model checking process.

We present several models of the protocol leader election protocol in the formal languages Promela [11] and Lotos [7]. Several properties have been checked with the model checking tools Spin [11, 12] and Xtl [22] (part of the Cæsar/Aldébaran distribution [6]).

We have found errors in the formal models with both Spin and Xtl. It turns out that some safety properties are not met by the protocol and that there are situations in which the protocol may never converge to a designate a leader. The cause of these errors is that the HAVi specification is not detailed enough to ensure that HAVi compliant implementations are faultless. The errors occur when communication between different devices is faster than communication between components in one device. Besides our conclusions on the correctness of the HAVi protocol, we compare the two model checking tools.

As far as we know, the only other paper in which HAVi leader election protocol between DCM Managers is studied is [28]. Here, a comparison is made between the performance of state space exploration of Spin and the  $\mu$ CRL tool set [8]. The model of the protocol differs from ours and no model checking is performed.

This paper is organised as follows. Section 2 gives an informal description of the HAVi leader election protocol. Section 3 introduces the tools and languages used. Section 4 describes our model of the protocol. Section 5 gives the details of all the model checking experiments. Finally, Section 6 gives several conclusions that we drew from this experiment.

In the appendices, relevant excerpts from the HAVi and 1394 specifications and several code listings can be found.

## Acknowledgements

I thank Eddy Zondag for his help in understanding and modelling the HAVi leader election protocol, Gerard Holzmann for his help with running Spin on large machines, Radu Mateescu for his help with Cæsar, Aldébaran and Xtl, and Yaroslav Usenko for questioning the validity of my models. Dennis Dams and Gerard Holzmann are thanked for their help in understanding the finer details of the CTL versus LTL problem. Finally, I thank Ron Koymans, Izak van Langevelde and Frits Vaandrager for their comments on previous versions of this paper.

## 2 The DCM Manager leader election protocol

The DCM Manager leader election protocol is described in the HAVi specification [9] at page 160. The protocol tries to find a suitable leader for the actual task of the DCM Managers, which is performed in the autonomous operation phase. We only study the leader election phase.

The parts of the HAVi specification and the IEEE 1394 standard that are relevant for this protocol are listed in Appendices A and B. Here, we give an informal explanation of the protocol, and the services that it requires from several HAVi components.

#### 2.1 Protocol

Each DCM Manager enters the leader election phase upon initialisation and each time a bus reset event is received. First it obtains information on the current network topology, by sending a request to another HAVi element, the Communications Media Manager, which returns a list with all the devices that are active in the (1394) network. The list contains the Global Unique ID (GUID) of all devices in the network. The DCM Manager then questions the 1394 level of each active device to find out some more information. The information needed for this protocol is the HAVi type of the device is (FAV, IAV, BAV or LAV), and whether there is a DCM Manager present at the device (at FAV compulsory, at IAV optional). Based on this information, the DCM Manager selects an initial leader from the GUIDs of devices on which a DCM Manager is present. Since each DCM Manager uses the same procedure for the selection, all of them choose the same initial leader without communicating with each other. Each DCM Manager which is not the initial leader is called initial follower.

The initial leader waits for initialisation requests from all initial followers, in which they state their capability. Using this new information and the HAVi type of the devices, the initial leader decides which DCM Manager is the best candidate for the final leadership. One of the criterions is the HAVi controller type, which is found in the (static) information of the HAVi device and which can be accessed from outside the device. The other criterion is Internet access which is found in the request messages from the followers. Each initial follower is informed of the decision with an initialisation reply, and the DCM Manager which has been elected as final leader is informed last. After this, the leader election phase ends and the autonomous operation phase phase is entered. Here, each DCM Manager which is not the final leader is called final follower.

During or after the leader election phase, the network topology may change, which causes a bus reset phase to start. Whenever this happens, the DCM Managers should start anew with the leader election because the previously elected leader may have disappeared from the network or a more suitable candidate may have appeared. The DCM Managers are informed of a bus reset phase by the Communications Media Manager with an event. The HAVi specification does not lay down any implementation rules for the delivery of this event, such as timing requirements. So it is possible that the bus reset event is delivered after the bus reset phase has already ended. If multiple bus reset phases occur (almost) adjacently, the DCM Managers may get out of phase in their leader election. Then one DCM Manager might be sending its initialisation request to an initial leader which is not aware of any bus reset phase having taken place, or vice versa. To keep things in order, the DCM Manager which is to be the initial leader, must remember this role and answer initialisation requests

3. Languages and tools 5

with an initialisation reply, even after leader election has ended. During and after the protocol, all unexpected messages are ignored.

## 2.2 HAVi components

The DCM Managers use the services of the local elements Messaging System, Communication Media Manager, and Event Manager. These elements will be available at each HAVi device that contains a DCM Manager.

The Messaging System provides two services and two modes of sending messages to software elements, whether local or not. The service choices are to block while waiting for a response by the receiver or not to wait for a response. The modes are reliable or simple. The reliable mode implicates that the sender is informed by the Messaging Systems involved whether the message reached the receiver. The sender is blocked until such an acknowledgement arrives or a time-out occurs. The simple mode implicates no acknowledgement information from the Messaging Systems is given to the sender. The Messaging System on the device of the receiver delivers the message to the receiver via a call back function, which the receiver has dispensed to the Messaging System at start-up time. The Messaging System uses the 1394 network for the actual message passing. From the 1394 specification we learn that at the 1394 level, no messages can be sent between different devices while a bus reset is taking place.

The DCM Managers communicate with each other using the reliable method and the response service. The HAVi specification does not limit the nature of the call back function that the DCM Managers use. The DCM Managers use a timeout of 3 seconds on all messages.

The **Event Manager** accepts requests to post events and sends a message with the event through the Messaging System to every local software element that has subscribed to the event. A posting request must be sent through the Messaging System. The DCM Managers all subscribe to the BusReset event during initialisation.

The Communication Media Manager provides information on the network configuration which it gets from the 1394 layer. Upon the start of a bus reset phase, it posts the event BusReset. Since each FAV or IAV device has its own Communication Media Manager to signal the bus reset start, the BusReset event only needs to be sent to software elements on the same device. This means that the Messaging System can at all times deliver the messages containing this event to the interested parties, as long as the device is powered up.

The Communication Media Manager also allows software elements to request network information in the form of a GUIDList. This service is only available outside bus reset phases, after the Communication Media Manager has received the information from 1394. This information is to be asked with a message through the Messaging System.

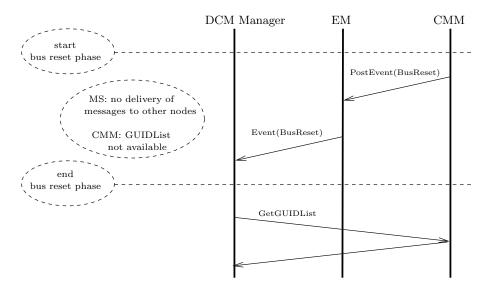

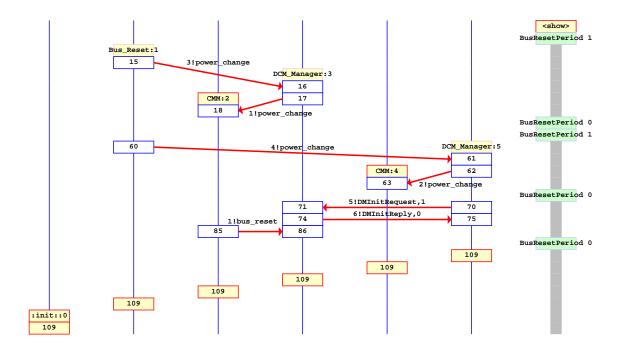

An example scenario In Figure 1 we show an example scenario in the following happens. A bus reset period starts. The Communication Media Manager posts the BusReset to the Event Manager. The Event Manager delivers the BusReset to the DCM Manager. The DCM Manager reacts by requesting the GUIDList from the Communication Media Manager. This list is available only when the bus reset period has ended.

## 3 Languages and tools

This section gives a short introduction to the languages and tools used for formalisation and verification of the leader election protocol. For details we refer to the documentation cited below.

3. Languages and tools 6

Figure 1: A bus reset scenario

## 3.1 Spin and Promela

Spin [11, 12] is a tool that supports simulation and verification of Promela [11] models of distributed systems. Models in Promela (a Process Meta Language) consist of definitions of process behaviour, with variable assignments, sequential and alternative composition, repetition and dynamic process creation. Communication between processes happens on synchronous or asynchronous channels. Synchronous communication always involves two processes. The support of data types is very limited: basic types are booleans and naturals, from which arrays and record structures can be built.

Verification is supported through detection of deadlocks, invalid end-states or non-progress loops, through violation of assertions and through LTL [24, 20] properties. The verification is done on the fly: the global state space is not constructed, but explored directly from an interpreted version of the Promela code.

## 3.2 Lotos, Cæsar/Aldébaran and Xtl

Lotos [7] is a standardised language for abstract modelling of distributed systems. Lotos models consist of a data part and a behaviour part: the data part is expressed in ACT-ONE, an algebraic formalism for abstract data types, and the behaviour part is expressed in process algebra with sequential, alternative and parallel composition, and recursion. Communication happens on synchronous gates and can involve more than two processes.

The Cæsar/Aldébaran tool set [6] facilitates simulation and verification of Lotos models. Simulation and detection of deadlocks, livelocks et cetera can be done on the fly.

The Xtl tool [22] (which is part of the Cæsar/Aldébaran tool set) facilitates the verification of temporal properties over Lotos models. First the global state space must be generated (with Cæsar), then Xtl can verify a property given in one of the following logics: HML [10], CTL [1], LTAC [26], ACTL [4, 3] and the modal  $\mu$ -calculus [18]. It is even possible to define one's own modal logic in terms of the libraries provided by Xtl (including greatest and least fixpoint operators).

## 4 Modelling decisions

In this section, our model of the protocol is explained. What is presented here is the result of a process of experimenting with different models, imposing and lifting restrictions until a satisfactory model with a manageable size was obtained.

First we explain the general modelling decisions, and give a description of the processes involved. Then the details of the Promela and Lotos models are explained (See Appendices C and D for code listings). Unless stated otherwise, the explanations refer to the model of the protocol with 3 DCM Managers and asynchronous communication between the DCM Managers. In the remainder of this section we abbreviate DCM Manager (DM), Communication Media Manager (CMM), and Messaging System (MS).

#### 4.1 General description

**Restrictions on the network** Each of the following choices is a restriction on what is allowed by the HAVi model. These restrictions are imposed in order to obtain a model of manageable size.

We study only situations with one network in which maximally three devices are active, and demand that in the start state no device is powered on.

The HAVi device types are FAV, IAV, BAV and LAV. We assume that there only are FAV devices in the network, and that on each of these devices there is a DM present.

A bus reset in the 1394 network may be caused by a change in the network topology (a device being added to or removed from the network), by a device in the network being powered up or down, by race conditions in the 1394 protocol or by other error situations. We model the cause of a bus reset as the power change of zero or more devices in the network. Here, zero power changes represents some other cause of bus reset, and the power change of a device also represents the connecting or disconnecting of that device (when a device is disconnected but still powered up, it operates in a new network consisting of just itself; we only study one network). The network behaviour is modelled with the process Bus\_Reset.

From IEEE 1394 we learn that the worst-case time delay between the start of the bus reset phase and the moment that the last device in the network notices the bus reset is less than 167 microseconds. The duration of the bus reset phase until normal operation resumes is at least 414 and maximally 581 microseconds. We restrict the bus reset phase delay to zero, which means that the bus reset phase starts at the same time at all devices in the network. For our verification purposes we only want to consider properties that concern situation in which a bus reset is not taking place. Therefore it is convenient to have the start of the bus reset phase actually precede the change of network which causes the bus reset phase.

In the HAVi design, each DCM Manager use a capability and a preference in the leader election protocol. We restrict ourselves to the capability UrlCapable, which indicates whether a device has Internet access (true) or not (false). We assume that the value of UrlCapable does not change.

In a 1394 network a device may be unplugged (powered off), and then plugged back in (powered on). This may cause the device to get a different 1394 physical ID and HAVi SEID (Software Element ID) once it is back in the network, than the 1394 and HAVi IDs it had before. Since each device has a globally unique ID (GUID) which does not change, and other devices can find out about this through the GUIDList which is managed by their CMM, we only identify devices with their GUID and do not model the physical ID.

Which HAVi components? We model the DM, the MS and the CMM with separate processes, which are described below. We do not include a process for the Event Manager. The only event posted to this component will be the BusReset, and all different scenarios of delivery of this event can be modelled by one synchronous communication between the CMM and the DM. If the delivery is unsuccessful, the communication does not occur. An extra process Bus\_Reset is needed to model

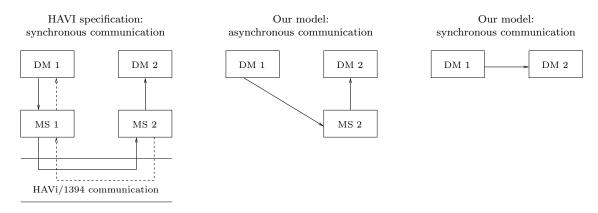

Figure 2: DCM Manager to DCM Manager communication

the behaviour of the 1394 network.

**Process Bus\_Reset** This process determines whether a new bus reset period will start, and which devices (hence which DMs and CMMs) will be powered up or down. Both of these choices are non-deterministic, hence in a verification all possibilities will be considered. Whenever a device is powered up or down, the DM, CMM and MS on that device are informed by Bus\_Reset in a synchronous manner. The power changes are determined in increasing order of device ID.

**Process CMM** This process controls the GUIDList, in which all devices present in the network are listed. It also signals any start or end of a bus reset period on the 1394 network, and passes this information on to the DM and the MS on the same device.

When several bus reset periods follow each other with little time in between, it is possible that a CMM has not posted the occurrence of a previous bus reset, when the next is already taking place. The HAVi specification does not define whether both bus reset events should be posted or just one. We choose to have the new bus reset overrule the previous one, and have only the last bus reset notification being posted and delivered.

**Process MS** This process takes care of the communication between the DMs and acts as a buffer. All message transfers that use the MS, are performed in reliable mode, therefore we model such a message transfer as one communication involving just the sending and the receiving component. The message transfer is shown in Figure 2. The HAVi design is that DM 1 sends a message, intended for DM 2, to the MS 1 (which is on the same device as DM 1). MS 1 sends the message on the network to MS 2, which delivers it to DM 2. After sending the message, DM 1 will wait for an error message or an acknowledgement of successful delivery to DM 2. DM 1 only continues its operation after such a notification. In Figure 2, continuous arrows show how a message is transported through the HAVi architecture from DM 1 to DM 2, and the dashed arrows show how the notifications are generated and returned. In case of erroneous transfer, the message may not reach MS 2 or DM 2. Successful delivery to DM 2 means that either DM 2 is interrupted to receive the message (synchronous communication) or the message is put into a buffer designated by DM 2 (asynchronous communication). We have modelled the synchronous version of this communication with direct synchronous communication between DM 1 and DM 2 (and then there is no need for any MS process), and the asynchronous version by synchronous communication between DM 1 and MS 2. In the latter case, DM 2 can get the message from MS 2 by synchronous communication. Note that MS 1 is not used in this communication scheme. This modelling choice is made to limit the possibilities for the communication, which is reasonable

since we are only interested in the communication succeeding (modelled by the message put into the buffer) or failing (modelled by the communication not occurring at all). Of course, the size of the buffer maintained by the MS limits the number of messages that can be sent to a DM before it actually receives them.

So, in short, in the case of synchronous communication between DMs, there will be no MS process in our model. In the case of asynchronous communication between DMs, there will be an MS process which acts as a buffer for incoming messages directed to the DM at the same device. The buffer size is a parameter for the model; in all our models the buffer size is 1. In case of asynchronous communication, the DM will empty the buffer in the event of a bus reset period or whenever the power is switched off.

**Process DCM\_Manager** The general task of the DM is explained in Section 2. Our model follows this procedure as closely as possible, except for a few modelling choices.

- 1. In our model we skip the subscription that the DM uses to inform the EM that it wants to receive all bus reset events. We also skip the registration of the call back function that the DM must dispense to the MS.

- 2. From the two parameters that the DM uses in the protocol, we only consider UrlCapable (Internet access).

- 3. The HAVi method of electing the initial leader, is to choose the DM on the device with the highest bit order reversed ID. Since our assignment of IDs to DMs is arbitrary, we just choose the DM with the lowest ID for initial leader.

- 4. The selection of the final leader in the HAVi design should be an arbitrary choice of the devices with the best capabilities. We study networks with only FAV devices on which a DM is present, hence we let the device with the lowest ID and UrlCapable set to true be the final leader (which is not arbitrary, but does limit the size of the state space). If no device has special capabilities, the HAVi design allows the initial leader to elect an arbitrary device for final leader. In this case, we have the initial leader elect itself for final leader (which also limits the state space size).

- 5. In the HAVi protocol, each initial follower will send its initialisation request to the initial leader, and will resend the request if a reply was not received before a timeout occurs (which is after 3 seconds). All our models are without timing information. Hence we let the initial follower choose arbitrarily between resending the request and receiving the reply. In this manner we cover all possibilities. Note that this choice does not introduce new behaviour, that is, behaviour that is not permitted by the HAVi specification.

#### 4.2 Promela

The Promela code is listed in Appendix C.1.

At the beginning of the code, some type definitions are given for the global variables in which all information about the several DMs is stored. These variables must be global (as opposed to local for the DCM\_Manager process that actually 'owns' the information) in order to facilitate access to this information in the model checking process. Then some channels are defined which are used for communication between DMs (asynchronous in this model), between DM and CMM (synchronous), and between DM and the Bus\_Reset process. We have chosen to model the asynchronous communication between DMs with the channel chanDM, and not a separate MS process. This helps in keeping the model simple and the state space small.

The statement labels indicate the state a process is in. By default, execution of a process starts at the first statement. When a change of state is desired, this is done with the goto <label> statement, where <label> is the target state.

Many statements in the processes are not meant to be executed in an interleaved manner with other activities in the network. With the atomic attribute, we can express that the statements in its scope are to be executed without creating new states in between. This also helps in keeping the state space small.

Most of the processes should be interrupted when the power on the corresponding device is switched off. This interruption is modelled with the operator unless.

**Process Bus\_Reset** First a bus reset period is started. The decision to actually execute this statement is made non-deterministically, meaning that in the whole state space it is always possible to postpone this branch of execution as long as there is another statement that can be executed.

The start of the bus reset period is forwarded to all the CMMs that are up, by setting the corresponding delivery boolean in the global BusResetDelivery array. If this boolean was true already because a previous bus reset was not handled yet by a CMM, the boolean will remain true, so only the last bus reset notification is delivered.

Whenever a device is powered up or down, a power\_change message is sent to the corresponding DM, which will in its turn inform the CMM. If Promela supported multi-way communication, both DM and CMM could be informed at the same time. As it is, this modelling choice keeps the size of the state space manageable.

The model in Appendix C.3 allows maximally two bus reset periods. This makes the behaviour of the model finite and allows us to search for invalid end states. The reason for this is given in Section 5.4.

**Process CMM** Whenever the device of the CMM is being powered up or down, it will get a message on the (synchronous) channel chanCMM and goto the corresponding state. Whenever the device of the CMM is up and the start of a bus reset period is marked in the delivery variable in the global array BusResetDelivery, then the CMM forwards this information to the DM on the same device, by means of a message on chanCMM, which will interrupt the DM.

The control of the GUIDList is not done explicitly by CMM, since it is not possible to send the list on a channel (because Promela forbids the sending of array structures). Instead, we have the DMs read a global variable, which is permitted only outside bus reset periods.

**Process DCM\_Manager** This process actually performs the tasks of the leader election protocol. If it becomes initial leader, it needs a local array for keeping track of information received from initial followers. This information is stored the array InfoHost. When the power of the device is not on, the process just waits for a message that power has been turned on. When this happens, it forwards the information to the local CMM (which is one of many ways to solve the multi-way synchronisation which is not provided by Promela), and starts the leader election protocol.

First the DM needs the contents of the GUIDList. This list can be obtained as soon as the latest bus reset period has ended. The information from global array Global is copied into the appropriate entry of global array Local (this entry is owned by this process; the array is global only for model checking purposes). From the GUIDList, the initial leader is determined. The DM continues being either the initial leader, or an initial follower.

Being the initial leader is not kept track of in a variable in this model. Only final leadership is recorded in a fleader variable for each DM. The model in Appendix C.2 records both kinds of leadership in a leader variable for each DM. Which model is used during verification depends on the property that is to be checked,

The initial leader and follower tasks are described in Section 2.

The final leader and followers should perform the tasks of the autonomous operation phase, but we have not modelled this behaviour. Therefore a final leader or follower DM does nothing, except wait for a new bus reset period, a power change or (in case it was the initial leader) answer initialisation

requests with the initialisation reply.

**Process MS** This process is not present in the Promela model. We choose to have the asynchronous channel chanDM perform the desired functionality. This decision forces us to put the awareness of a bus reset taking place (hence no communication on the network possible) in a different process. We choose to have the sending DM inspect the global variable BusResetPeriod.

**Process Init** Here, all the processes are actually started, and the non-deterministic choice for UrlCapable to be true or false is made. Note that the process Assertion is also started, which is not listed in the Promela model itself. This process monitors the property which is to be checked. The properties are explained in Section 5.

#### 4.3 Lotos

The Lotos code is listed in Appendices D.1, D.2 and D.3.

We will not explain the data parts any further, since they mostly speak for themselves.

As for the behaviour part, this is modelled with a process definition for each small part of the protocol's behaviour. Because of the cyclic character of the whole protocol and certain parts of it, recursion is often used in these process definitions. Cæsar does not allow some forms of recursion, which are part of Lotos, such as recursion in combination with a communication operator. This means that we cannot recursively instantiate the DM processes.

Most of the processes should be interrupted when the power on the corresponding device is switched off. This is done with the reception of a power\_change message at the right-hand side of the disrupt operator [>. This operator works as follows: (1) the process A [>B can perform an action from process A and then behave as A' [>B (with A' the remainder of A), and (2) A [>B can perform an action from process B and then behave as B' (with B' the remainder of B).

Because of the enforced multi-way synchronisation, a process must sometimes participate in a communication even if the power of its device is off. The subprocess FlushBusReset takes care of this.

Process LE This is the top process expression which initialises all the subprocesses that are to communicate with each other. In the initialisation of this process, the network consists of 3 DMs that are not up. This parameter can then be passed to subprocesses. There are also gates, which are used for synchronous communication, which can be multi-way. For instance, process BusReset communicates over gate gBusReset with all instances of process CMM and of process MS. A communication from BusReset on this gate can only take place if all of the processes mentioned participate in it (enforced synchronisation). The instantiation of the DM processes is a non-deterministic choice between instantiation with UrlCapable set to either true or false.

**Process BusReset** As in the Promela model, the only option of this process is to start a bus reset period, but this choice may be delayed if there is any other activity in the network. Starting with ID 1, the subprocess BusReset2 decides non-deterministically for each device whether its power status changes or not. The operator + works modulo 4, so 3+1 yields 0, and at this ID the subprocess BusReset2 ends the bus reset period, and calls the top process again.

**Process CMM** The states of this process are reflected in the subprocesses CMMDown, CMMUp, CMMReady, CMMDeliver and CMMDeliver2.

Whenever CMMUp is executed, the CMM has to get the GUIDList first, which is available only at the end of the bus reset period. This information is sent by BusReset. After this, the CMM is ready for normal operation.

CMMReady is the normal situation when the CMM is up. It can send the GUIDList on gate gInfo to the DM with the same ID, or signal a bus reset start. After a bus reset start, the CMM executes CMMDeliver

In CMMDeliver two things must happen: an update of the GUIDList must be received from Bus-Reset, and a bus\_reset\_event must be sent to the DM on this device. If the message to DM is sent first, then all the CMM can do is wait for the reception of the new GUIDList, after which it is ready for normal operation. If the bus reset period ends before the message to DM is sent, the process CMMDeliver2 is executed.

In CMMDeliver2 the GUIDList is available again for the DM on this device, the bus\_reset\_event must be sent to the DM, and a new bus reset period may start.

At any point in this behaviour, the power of the device may be switched off, which is handled with the disrupt operator [>.

**Process MS** The states of this process are reflected in the subprocesses MSDown, MSUp, MSSuspend, and MSReady. Of these we only explain the latter two.

MSSuspend is executed whenever the MS is up, but a bus reset is taking place. No communication is possible on the network, but the DM at the same device may still receive messages from the buffer. This state is left as soon as the bus reset period ends.

MSReady is the normal situation when the MS is up.

At any point in this behaviour, the power of the device may be switched off, which is handled with the disrupt operator [>.

**Process DCM\_Manager** The states of this process are reflected in the subprocesses DMDown, DMUp, DMif, DMSendRequest, DMil, DMElect, DMSendReply, DMff, DMffi, DMffi and DMfli.

In DMUp, the leader election process starts. The DM gets the GUIDList from the CMM on the same device, and uses the function i\_leader to compute the initial leader.

In DMif and DMSendRequest, the initial follower's actions are executed (See Section 2).

In DMil, DMElect and DMSendReply, the initial leader's actions are executed (See Section 2).

In DMff, DMffi, DMfl and DMfli, the final leader and followers should determine resource allocation of the DCM units in the network, but we have not modelled this behaviour. Therefore a final leader or follower DM does nothing, except wait for a new bus reset period, a power change or (in case it was the initial leader, which is in DMffi and DMfli) answer initialisation requests with the initialisation reply.

At any point in this behaviour, the power of the device may be switched off, which is handled with the disrupt operator [>.

## 5 Model checking experiments

In order to check that the protocol works as intended, we have checked four properties on several models of the protocol. Each of the following sections is dedicated to one property. The properties are listed in this section in an informal manner and in a notation slightly different from the actual input for the tools. For the exact definitions of the properties, we refer to the Appendices C.5, D.4 and D.6.

The properties presented here were devised after the models of the protocol had been constructed. This has both advantages and disadvantages. A disadvantage is that it turns out to be rather difficult to express properties for our specific models. In fact we have had to change them slightly to make some information visible. An advantage is that the models have not been tailored towards the properties that should be checked except the changes mentioned. A potential danger is that the the model does not resemble the protocol close enough anymore, and the properties to be checked trivially hold.

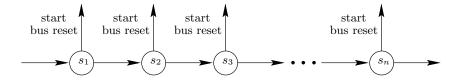

Since the behaviour of the protocol is unpredictable during bus resets or the period that the CMMs need to deliver the bus reset event, we only demand that the properties be true for stable situations, that is, in states where it is not the case that a bus reset is taking place or a bus reset event should still be delivered. Since a new bus reset period may start at any moment after the previous bus reset has ended and since we have included this possibility in our models with non-deterministic choice, we get the behaviour depicted in Figure 3 from our models. Suppose that  $s_1, s_2, s_3, \ldots, s_n$  in Figure 3 are stable states, which means that no bus reset is taking place, and all events concerning the last bus reset have been delivered. We see that from  $s_1$  it is possible that a new bus reset period starts, but it is also possible that some other behaviour takes place on the transition to  $s_2$ . If we establish a property in terms of behaviour, we can only capture the desired behaviour from  $s_1$  by using an exists quantifier: from  $s_1$  there exists a behaviour which satisfies a certain requirement. Moreover, in our models the amount of activity that concerns the protocol is bounded. After a certain point, the protocol is stuck or completed, and the only possible behaviour is that a new bus reset period starts. So it is not possible to express a property as follows: "for all behaviours: if no bus reset starts in this behaviour then fulfill a requirement".

**Expressing properties for Promela models** Safety properties can be checked in Spin through the use of assertion statements. We use a process with only such an assertion statement in the verification for checking whether there is a state in which the assertion is false. If this happens, Spin reports this as an error and stops the verification. An error trace is saved which can be used for diagnostic purposes.

Liveness properties can be checked in Spin through the use of LTL [24, 20] formulas, which are translated into **never** claims. A never claim is a process which will only terminate if the corresponding LTL formula was violated. Actually, never claims represent  $\omega$ -regular properties. Spin checks whether never claims hold in the initial state. This means that if the never claims is already satisfied by the initial state, no further exploration of the state space is needed.

Both assertions and LTL formulas are expressed in terms of predicates, which range over values of variables. It is also possible to check a pattern of communications, but not in combination with checks of state variable values. Since in our case, it is by far easiest to find error situations by referencing the state variable values, we stick to the assertions and never claims.

**Expressing properties for Lotos models** We express safety and liveness properties in ACTL [4, 3] for the verification of the Lotos models is done with A property is checked by Xtl on the reachable state space, by checking for each reachable state whether the property holds in that state.

Since the model checker Xtl is only used on state spaces which have been generated from the Lotos model, the information of state variables is lost. Actually, the states are identified by natural numbers in the state graph accepted by Xtl. This means that we cannot express properties in terms of values of state variables, and we can just observe the occurrences of actions. A consequence of this approach is that safety properties can only be expressed as liveness properties. With the ACTL logic we are able to observe certain patterns of occurrences of actions. In order to still reference state variable values, one could build self-loops into the Lotos model. which give the values of the state variables in

Figure 3: Protocol behaviour

that state. However, this was not a feasible approach in our case.

An action can observed by comparing an action label from a transition to a label set in the property that is being checked. Comparing an action label to the label set  $\mathbf{T}$  ( $\mathbf{F}$ ) always succeeds (fails). Label sets can be constructed from syntactic expressions that capture one or more action labels, and boolean operators. For instance, it is straightforward to construct a label set that succeeds when compared to the label BUS\_RESET\_START or the label POWER\_CHANGE and fails otherwise.

In order to enable the checking of not just communications between the DCM Managers, but also other important actions, the model contains a few extra observable events. These the occurrences of communication on the special gate **GEvent**. In this way we observe a DCM Manager electing itself for initial or final leader.

We now give an overview of the ACTL operators used, and their informal meaning<sup>1</sup>.

$\mathbf{T}, \neg, \wedge, \vee, \rightarrow$  Boolean true, negation, and, or, implication

$[a] \phi$  For every transition  $s \xrightarrow{a} t$  from the current state: formula  $\phi$  must hold in the target state t

$\forall \mathbf{G}_a \phi$  For each (possibly finite) path from the current state where all actions are either a or  $\tau$ , formula  $\phi$  must hold in every state

$\exists (\phi_a \mathbf{U}_b \psi)$  There exists a path from the current state along which for a finite fragment formula  $\phi$  holds in each state and all actions are either a or  $\tau$ , and this fragment is immediately followed by a transition  $s \xrightarrow{b} t$ , and in state t formula  $\psi$  holds.

For a complete list of ACTL operators and a formal definition, we refer to [10, 4, 3].

The standard library in the Cæsar/Aldébaran distribution for using these operators is the actl.xtl library (implemented by Mateescu [22]) which establishes the validity of a formula by checking whether the formula holds in all reachable states of the Lotos model. This library is not implemented in such a way that it gives diagnostics in case a property is not true. Diagnostics can be obtained by using the walk\_actl.xtl library (implemented by Pecheur [23]), which also implements the ACTL operators mentioned, and which tries to find an error trace. This implementation establishes the validity of a formula by checking whether the formula holds in the initial state of the Lotos model. Of course, in general the use of this library is more costly since there is more administration involved in finding the trace, and a lot of backtracking occurs.

#### 5.1 Safety: At most one leader

It is never the case that more than one DCM Manager is a (initial or final) leader.

Spin We use an assertion statement, and check the following formula:

$$\forall d, d'. (\neg bus\_reset \land leader(d) \land leader(d') \rightarrow (d = d'))$$

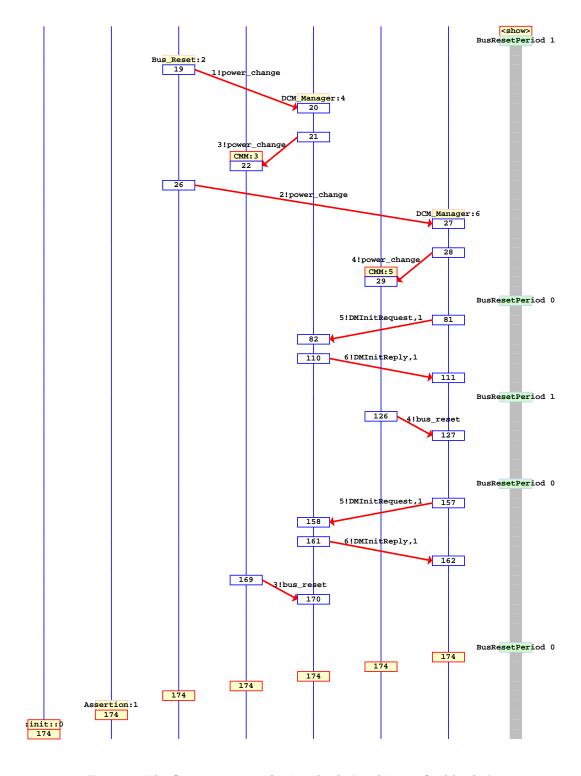

This property does not hold for any of the models. It turns out that the error trace found by Spin for the property checked in Section 5.3 is also an error trace for this property. See Figure 4 for the trace and Section 5.3 for an explanation. In Section 5.5 we discuss whether the HAVi protocol is wrong.

Xtl What we want to establish, is that there are not multiple InitialLeader or FinalLeader events in between bus reset periods. Since we can check for patterns of actions, we formulate the property as follows: if a bad pattern of Initial or FinalLeader events occurs, then we are not in a stable situation (where no bus reset is taking place and the last bus reset events have all been delivered). This boils

<sup>&</sup>lt;sup>1</sup>Note that the [] operator does not have the ACTL interpretation, but the interpretation of the Hennessy-Milner modal logic [10]. Since the Xtl library for ACTL is defined using the Xtl libraries for the Hennessy-Milner modal logic and the modal  $\mu$ -calculus [18], we can use operators from these logics in any ACTL expression

down to expressing that when a bad pattern does occur outside bus reset periods, apparently a bus reset event must still be delivered.

We check the following formula:

```

\begin{split} ([b_1] \, \forall \mathbf{G}_{i_1}([i_3] \, \forall \mathbf{G}_{i_1}([i_3] \, \exists (\mathbf{T}_{i_2}\mathbf{U}_{b_2}\mathbf{T}))) \, \wedge \, ([b_1] \, \forall \mathbf{G}_{i_1}([f] \, \forall \mathbf{G}_{i_1}([i_4 \cup f] \, \exists (\mathbf{T}_{i_2}\mathbf{U}_{b_2}\mathbf{T}))) \\ \text{where} \quad b_1 = BusResetEnd \\ \quad b_2 = BusResetEvent \\ \quad i_1 = Ignore_1 = \neg (BusResetEvent \vee BusResetStart \vee Initleader \vee FinalLeader) \\ \quad i_2 = Ignore_2 = \neg (BusResetEvent \vee BusResetStart) \\ \quad i_3 = InitLeader \\ \quad i_4 = InitLeader \vee FinalLeader \\ \quad f = FinalLeader \end{split}

```

This formula expresses two patterns that should be followed by a bus reset event being delivered. Both patterns start with the end of a bus reset period, and do not allow the start of a new bus reset period by the use of the action label sets Ignore<sub>1</sub> and Ignore<sub>2</sub>. The first pattern checks the double occurrence of the InitialLeader event. The second pattern checks the occurrence of a FinalLeader event, followed by either an InitialLeader or FinalLeader event. The action label sets in the subscript of the **G** and **T** symbols enable the actions in the subscripts to occur in any sequence in between.

This property holds for all models. Since we found errors in the Promela models for this property using Spin two questions remain, namely whether the error behaviour found with Spin also occurs here and if so, why it is not found with the ACTL formula used. Simulating the behaviour from the Spin error trace is possible for the Lotos model with two DCM Managers and synchronous behaviour. As to the second question. The answer is that the label set Ignore<sub>1</sub> is too restrictive. The idea of checking a pattern when a bus reset event has completed turns out counterproductive. We might have checked all occurrences of the FinalLeader event followed by bad patterns, and qualified the occurrence of a BusResetStart, BusResetEnd or BusResetEvent as a good pattern. In any case, it appears that the formulation of the property in this setting is very complicated. In Section 5.5 we discuss whether the HAVi protocol is wrong.

#### 5.2 Safety: Best candidate becomes final leader

It is never the case that a final leader is selected which is not UrlCapable, while there is a DCM Manager active in the network which is UrlCapable.

**Spin** We use an assertion statement, and check the following formula:

```

\neg bus\_reset \land \forall d.((f\_leader(d) \land \neg url\_capable(d)) \rightarrow \forall d'.(up(d') \rightarrow \neg url\_capable(d')))

```

This property holds for all models except for the setting with three DCM Managers and asynchronous communication. However, the error found here reveals problems with the interpretation and execution of the Promela code rather than an error in the protocol. In fact, we can reason why in our model the property should be true for any number of DCM Managers with either synchronous or asynchronous communication. The idea is that upon receipt of a bus reset event, each DCM Manager will clear the information of being final leader and ask for the new network topology (the GUIDList). Since the start of a bus reset period causes the delivery of a bus reset event at some time, in a stable situation all bus reset events have been delivered, and each DCM Manager must have the correct network topology information. So after the last bus reset event delivery to a DCM Manager, it cannot choose a non UrlCapable final Leader if there is a UrlCapable DCM Manager present. So the only way in which a

non UrlCapable DCM Manager can still be the final leader in a stable situation, while a UrlCapable DCM Manager is present, is to receive an InitReply with its identity from the initial leader, when the initial leader has not received the latest bus reset event. But we have modelled the final leader election by having the initial leader choose itself, if no UrlCapable Manager is present. So it cannot ever send an InitReply with the identity of another, non UrlCapable DCM Manager. It is clear that although the property must hold in our models, it does not hold when we lift the restriction that the initial leader chooses itself for final leader when no UrlCapable DCM Manager is present. In Section 5.5 we discuss whether the HAVi protocol is wrong.

Xtl The situation that a DCM Manager is up and UrlCapable is signalled by the request from such a DCM Manager to the initial leader, in which the UrlCapable parameter is true. Whenever such a request is followed by the election of a final leader which is not UrlCapable, there must be a bus reset event pending that needs to be delivered.

We check the following formula:

```

[u] \ \forall \mathbf{G}_{i_1}([f] \ \exists (\mathbf{T}_{i_2}\mathbf{U}_b\mathbf{T})) where b = BusResetEvent i_1 = Ignore_1 = \neg (BusResetEvent \lor BusResetStart \lor BusResetEnd \lor FinalLeader) i_2 = Ignore_2 = \neg (BusResetEvent \lor BusResetStart) f = FinalLeaderNotUrlCapable u = RequestUrlCapable

```

This property holds for all models. See the paragraph above on Spin experiments for this property, for a discussion whether this property holds in general or not. In Section 5.5 we discuss whether the HAVi protocol is wrong.

## 5.3 Safety: All agree on the final leader

Whenever a final leader is selected, all DCM Managers agree on the identity of this leader. Of course this can only be checked as soon as all DCM Managers have been informed of the decision of the initial leader. Since the final leader is informed last of the decision (and whenever this happens to be also the initial leader, it will 'inform itself last'), this can be checked as soon as one of the DCM Managers has been elected for final leader.

**Spin** We use an assertion statement, and check the following formula:

```

\forall d. (\neg bus\_reset \land f\_leader(d) \rightarrow \forall d'. (up(d') \rightarrow leader\_id(d') = d))

```

This property does not hold for any of the models. In Figure 4 an error trace constructed by Spin for the model with two DCM Managers and synchronous communication is listed. This trace describes the following behaviour. In the first bus reset period both DCM Managers are powered up. They start leader election, in which DCM Manager A is the initial leader and DCM Manager B is the initial follower. B is UrlCapable and A is not. B sends A an InitRequest, A computes the final leader which is B, and sends the InitReply to B. A new bus reset period starts and ends without change in the network topology. The CMM on the device of B delivers the bus reset event to B, and B starts afresh with the leader election. B is again initial follower and sends A an InitRequest. A does not know about the second bus reset period so it is in its final follower phase where it answers any InitRequest with the same InitReply as before. A sends B the InitReply and B concludes it is the final leader. Now the CMM on the device of A delivers the bus reset event to A, and A starts afresh with the leader election. A is again initial leader and does not know the identity of the final leader to be elected, while B still thinks it is final leader. In this state the property checked is violated. In Section 5.5 we discuss whether the HAVi protocol is wrong.

Figure 4: The Spin error trace for 'one leader' and 'same final leader'

```

AG_A(A, F) is FALSE

0 : (0, "GBUSRESET !BUS_RESET_START", 5036)

1 : (5036, "GUPDOWN !1 !POWER_CHANGE", 3437)

2 : (3437, i, 4798)

: (4798, "GBUSRESET !BUS_RESET_END !CONSNET(CONSN(TRUE),CONSN(FALSE))", 4797)

: (4797, "GINFO !1 !GUID_LIST !CONSNET(CONSN(TRUE),CONSN(FALSE))", 4790)

: (4790, "GBUSRESET !BUS_RESET_START", 4789)

: (4789, "GEVENT !INIT_LEADER !1", 4769)

: (4769, i, 133)

: (133, "GUPDOWN !2 !POWER_CHANGE", 142)

: (142, "GBUSRESET !BUS_RESET_END !CONSNET(CONSN(TRUE),CONSN(TRUE))", 658)

10 : (658, "GEVENT !FINAL_LEADER !1 !FALSE", 150)

11: (150, "GINFO !2 !GUID_LIST !CONSNET(CONSN(TRUE), CONSN(TRUE))", 2542)

12: (2542, "GDMOUT !1 !CONSM(DMINITREQUEST,2,TRUE)", 552)

13: (552, "GDMIN !1 !CONSM(DMINITREQUEST,2,TRUE)", 2524)

14: (2524, "GDMOUT !2 !CONSM(DMINITREPLY,1,FALSE)", 316)

15 : (316, "GINFO !1 !BUS_RESET_EVENT", 303)

16 : (303, "GDMOUT !1 !EMPTY", 1924)

17 : (1924, "GDMOUT !1 !CONSM(DMINITREQUEST,2,TRUE)", 1921)

Box(A, F) is FALSE

18: (1921, "GDMIN !2 !CONSM(DMINITREPLY,1,FALSE)", 1909)

AG_A(A, F) is FALSE

19: (1909, "GINFO !1 !GUID_LIST !CONSNET(CONSN(TRUE), CONSN(TRUE))", 1486)

20 : (1486, "GEVENT !INIT_LEADER !1", 1662)

21 : (1662, "GDMIN !1 !CONSM(DMINITREQUEST,2,TRUE)", 1507)

Box(A, F) is FALSE

22: (1507, "GDMOUT!2!CONSM(DMINITREPLY,2,FALSE)", 1548)

EU_A_B(F, A, B, G) is FALSE

*Failure.*

```

Figure 5: The Xtl error trace for 'same final leader'

Xtl We can only check that everyone has the same leader identity by checking the parameters of messages/events concerning the final leader. We require the leader identity parameter to be equal for all such actions in stable situations. So the property must express that whenever two actions carry a different leader identity outside a bus reset period, apparently a bus reset event must still be delivered. We check the following formula:

```

\forall d. \ [l_d] \ \forall \mathbf{G}_{i_1}([l_{\neg d}] \ \exists (\mathbf{T}_{i_2}\mathbf{U}_b\mathbf{T})) where b = BusResetEvent i_1 = Ignore_1 = \neg (BusResetEvent \lor BusResetStart \lor BusResetEnd \lor InitReply \lor FinalLeader) i_2 = Ignore_2 = \neg (BusResetEvent \lor BusResetStart \lor BusResetEnd) l_d = (InitReply \lor FinalLeader) \text{ with leader identity } d l_{\neg d} = (InitReply \lor FinalLeader) \text{ with leader identity not equal to } d

```

This property holds only when communication between DCM Managers is synchronous. In the asynchronous case an erroneous initialisation reply may be lingering in someones input queue, after the corresponding bus reset event has been handled by the sender of the erroneous message. In Figure 5 an error trace constructed with the walk\_actl library is listed. The behaviour described by this trace is as follows. In the first bus reset period DCM Manager A is powered up. A is not UrlCapable. A starts the leader election and elects itself for initial leader. In the second bus reset period DCM

Manager B is powered up. B is UrlCapable. After the second bus reset, A has not received the bus reset event yet. A elects itself for final leader which completes the leader election. B elects A for initial leader and sends an InitRequest. A receives the InitRequest from the MS and sends an InitReply with its own identity for final leader. Now A receives the bus reset event and starts the leader election anew. B has not received the InitReply from the MS yet and sends a second InitRequest to A. Now B receives the InitReply from the MS and concludes that A is the final leader. A elects itself for initial leader, and receives the second InitRequest that B sent from the MS. A elects B for final leader and sends an InitReply with the identity of B for final leader. The property is violated.

Since we found errors for the Promela models with synchronous communication using Spin, two questions remain, namely whether the error behaviour found with Spin also occurs here and if so, why it is not found with the ACTL formula used. In Section 5.1 we have already simulated the error behaviour found by Spin and depicted in Figure 4 on the Lotos model with two DCM Managers and synchronous communication. As to the second question. The ACTL formula used only checks communication involving leader identities. Here we are really hampered by the fact that for the current Lotos models it is not possible to include state information in the formula. It turns out that in the synchronous Lotos models a bus reset event will appear in between the two events carrying a different leader identity. Since such a pattern is in general not erroneous, it is not possible with this approach to find the erroneous behaviour constructed with Spin. In Section 5.5 we discuss whether the HAVi protocol is wrong.

#### 5.4 Liveness: Eventually there will always be a final leader

Whenever there is at least one DCM Manager active in the network, there should eventually be a final leader. The property we check is whether from each stable state in which at least one DCM Manager is up there exists a path on which no bus reset period starts and a final leader is chosen. It may be argued that this property is too strong since it assumes that there exists a path on which bus reset periods can be delayed until after the election of the final leader. If the environment would violate this assumption, the property would be false even when the protocol was correct. There are two reasons for our approach. First, we know that in our models the choice between a bus reset period starting and any other activity is non-deterministic. So bus reset periods can be delayed as long as other activity is possible. Second, the alternative property to be checked would be: 'After the handing out of the GUIDList, each path leads to a new bus reset period or a final leader being elected'. This formula requires that during and after the leader election activity, the DCM Managers can perform idle/internal actions indefinitely, in order to distinguish between situations where leader election is interrupted by a bus reset period and situations where leader election does not terminate for some other reason, i.e. livelock rather than deadlock, since in case of a deadlock a bus reset period is forced to start. Moreover, the models already contain a livelock when there are more two initial followers of which one keeps sending InitRequests and the other never gets a turn. The problem with livelocks is that the property should then be checked under certain fairness aspects. This makes the situation increasingly complex, and we have chosen to stick with the first formulation.

**Spin** The only way to model a liveness property like this and have Spin check its validity, is with an LTL formula. We have been able to express this without too much trouble in ACTL, as can be seen below. However, the expressivity of LTL and branching time logics like ACTL is not comparable [27]. When we try to express the property to be checked in LTL and formulate it as follows, we get an expression which is not in LTL syntax:

```

\Box((\neg bus\_reset \land (\exists d.\ up(d))) \rightarrow \exists(\neg bus\_reset\ \mathbf{U} \neg bus\_reset \land \exists d.\ f\_leader(d)))

```

Because of the  $\exists$  operator, this is not an LTL formula. However, we do need an  $\exists$  operator to express the behaviour that the Promela models should have (See also Figure 3). The reason is that an LTL formula is interpreted to be true if and only if it holds for each behaviour of the model. So if it is only

Figure 6: The Spin error trace for 'always final leader'

possible to express desired or undesired properties for one behaviour. But the property that we desire to have is that there always exists a good path. The property that we desire not to have is that there is no state from which there are only bad paths. This cannot be expressed in LTL. This problem has been discussed via e-mail [2, 13], but no solution was found, other than to change the model such that there is a fixed number of bus reset periods, after which the network remains stable. Then Spin's capability to find invalid end states can be used to check that the protocol ends up with a leader, or identify a finite path as undesirable with LTL. A drawback of this approach is that it is not a priori clear how many bus reset periods should be allowed to obtain correctness for the more general model. However, we already found errors in the Spin models for other properties, and in the Lotos models for this property. In the Spin models, errors occur already after two bus reset periods. We have changed all models such that at most two bus reset periods can take place, and added labels to indicate what states in the model are valid end states. Then it turns out that all new models have an invalid end state, which indicates that the protocol ends without electing a final leader even though at least one DCM Manager is up.

In Figure 6 the error trace constructed by Spin for the model with two DCM Managers and synchronous communication is listed. This trace describes the following behaviour. In the first bus reset period DCM Manager A is powered up. The first bus reset period is immediately followed by a second, in which DCM Manager B is powered up. A and B are both not UrlCapable. After the end of the second bus reset period, A does not receive the bus reset event yet. Now both A and B start the leader election, in which DCM Manager A is the initial leader and DCM Manager B is the initial follower. B sends A an InitRequest, A computes the final leader which is A, and sends the InitReply to B. B concludes that A is the final leader which completes the leader election. Now the CMM on the device of A delivers the bus reset event to A, and A starts afresh with the leader election. A is again initial leader and waits for the InitRequest from B, while B has already completed leader election. Since there is no action possible we are in an end state, and since for A the leader election has not been

```

AG_A(A, F) is FALSE

0 : (0, "GBUSRESET !BUS_RESET_START", 962)

1 : (962, "GUPDOWN !1 !POWER_CHANGE", 72)

: (72, i, 1024)

: (1024, "GBUSRESET !BUS_RESET_END !CONSNET(CONSN(TRUE),CONSN(FALSE))", 1023)

: (1023, "GBUSRESET !BUS_RESET_START", 820)

: (820, i, 612)

: (612, "GUPDOWN !2 !POWER_CHANGE", 542)

: (542, "GBUSRESET !BUS_RESET_END !CONSNET(CONSN(TRUE),CONSN(TRUE))", 288)

: (288, "GINFO !2 !GUID_LIST !CONSNET(CONSN(TRUE), CONSN(TRUE))", 97)

: (97, "GINFO !1 !GUID_LIST !CONSNET(CONSN(TRUE),CONSN(TRUE))", 335)

10 : (335, "GEVENT !INIT_LEADER !1", 231)

11 : (231, "GDM !1 !2 !DMINITREQUEST !FALSE", 199)

12: (199, "GDM !2 !1 !DMINITREPLY !1", 995)

13 : (995, "GINFO !1 !BUS_RESET_EVENT", 95)

Box(A, F) is FALSE

14 :

(95, "GINFO !1 !GUID_LIST !CONSNET(CONSN(TRUE), CONSN(TRUE))", 1003)

EU_A_B(F, A, B, G) is FALSE

*Failure.*

```

Figure 7: The Xtl error trace for 'always final leader'

completed, it is an invalid end state. In Section 5.5 we discuss whether the HAVi protocol is wrong.

Xtl We check whether a DCM Manager is up in a stable state by observing the transaction in which the CMM hands out the GUIDList. We check whether a final leader is elected by observing the FinalLeader event. We demand that there exists a path from each GUIDList transaction on which no bus reset period starts and on which a FinalLeader event occurs.

We check the following formula:

```

[g] \exists (\mathbf{T}_i \mathbf{U}_f \mathbf{T})

where i = Ignore

g = GetGUIDList

f = FinalLeader

```

This formula does not hold for any of the models.

In Figure 7 an error trace constructed with the walk\_actl library is listed. By coincidence, the behaviour described by this trace is the same as the behaviour described by the error trace found by Spin for this property. See earlier in this section for an explanantion of the behaviour. In Section 5.5 we discuss whether the HAVi protocol is wrong.

#### 5.5 Is the HAVi protocol wrong?

The error traces given in Figures 4, 5, 6 and 7 show that either our model of the protocol or the HAVi specification itself must be wrong.

The error traces indicate that problems occur when the delivery of a bus reset event message is delayed beyond the duration of the sending and delivery of both a message and a response between different devices. In the case of synchronous communication, another cause of problems is the availability of the GUIDList before the delivery of the corresponding bus reset event.

If all assumptions and restrictions that we made in our model are correct, then these scenarios may occur in an implementation that is totally compliant with this version of the HAVi specification,

because of two reasons. First, the HAVi specification does not lay down how long messages may be on their way in the system. Second, the delivery of any event has to go through the Event Manager. The Event Manager may cause a delay of the event for several reasons. It is not known how many events the Event Manager may get due to a bus reset period, which need to be delivered, and in what manner these events are processed. Furthermore, there may be many components that listen to the bus reset event and in a sequential approach to delivery of the events, the DCM Manager may very well be the last of them to receive this message.

If our assumptions are not correct, then obviously it is hard to say whether the protocol would be correct or not. However, all of the assumptions we made are restrictions on configurations or scenarios permitted by the HAVi document which means that we only exclude some HAVi behaviour. So the error behaviour we found would almost certainly be present in a model with fewer restrictions. In fact, the chances are high that with fewer restrictions more erroneous behaviour could be found in the protocol. We already argued in Section 5.2 that lifting the restriction that the initial leader chooses itself for final leader when no UrlCapable DCM Managers are present, will lead to violations of the property 'the best candidate becomes final leader'. Other generalisations we could make are: several types of devices in the network, physical IDs that change, bus reset periods that start and end at different moments in different devices, no difference between processing of events and messages, et cetera. Also, it may still be the case that one or more of the software elements used for this protocol have a potential deadlock in their behaviour, and thus prevent the DCM Managers from completing their leader election.

Our conclusion is that for the HAVi leader election protocol to be correct (meaning that any implementation that complies with HAVi works correctly), the HAVi specification should have requirements added on the duration of delivery of events related to the duration of communication between devices. Since the disruption by bus reset periods makes it difficult to establish such requirements, we think the easiest solution is to establish real-time constraints on the duration of sending and processing messages and events, which are realistic for HAVi-compliant implementations. This information should then be checked in a timed formal verification. Since timed model checking is beyond the scope of this experiment, we cannot give an estimate of time bounds that would work, or say whether such time bounds exist.

#### 5.6 Statistics

The statistics for model checking the different models with the Spin tool set (version 3.2.4, version 3.3.0 beta-13 May 1999) and the Cæsar/Aldébaran tool set (Cæsar version 5.3, Aldébaran version 6.4, Xtl version 1.1) are given in Tables 1, 2 and 3. All experiments with Spin were done on an SGI IRIX64 6.5 machine with 42 Gbyte of memory. All Cæsar/Aldébaran experiments were done on a SUN Ultra 5\_10 SunOS 5.6 machine with 1 Gbyte of memory.

A few remarks are in order.

- Spin, Cæsar, Aldébaran and Xtl all generate C code which after compilation performs the state space generation, minimisation and/or exploration.

- The memory numbers mentioned in Table 3 indicate the amount of memory used by the verifier generated by Xtl in C code, compiled to executable form. However, C compilation takes at least 6 Mb. For the walk\_actl library, C compilation takes at least 12 Mb for the models with 2 DCM Managers.

- For the Spin experiments, the memory usage is provided in the output of Spin. Note that this is always a little higher than the memory usage observed with the UNIX command 'top'. For the Cæsar, Aldébaran and Xtl experiments, the memory usage is obtained by observing the outcome of the UNIX command 'top'.

- For all experiments, the timing information is obtained by the UNIX command 'time'.

• Normally, Lotos state space generation is done with Cæsar in the .bcg format, which is very compact. However, Cæsar does not always create the smallest state space possible, and for the models in this case this means that state space generation gets stuck at an unknown portion of the desired total, and fails due to lack of memory. So we turned to an alternative route, and generated the state spaces separately for each instance of each process in the main parallel composition expression. This again is done with Cæsar. The state spaces generated are first minimised with respect to strong bisimulation equivalence (with Aldébaran and the bmin criterion), which is also done in the .bcg format. Then these minimised state spaces must be combined into one state space. This is done with Aldébaran and works only if the separate state spaces are in the .aut format. The target state space is then also in the .aut format. The .bcg version is computed and then minimised.

When generating the state space for one of the communicating processes, often the receipt of a messages is not restricted other than by all possible instantiations of the parameters of the communication. These parameter values had to be restricted in the separate process definitions to make state space generation manageable. Without these restrictions, it was not possible to generate a state space for the DCM Manager process with the lowest identity, in the case of asynchronous communication and 3 DCM Managers.

- All state space generation sizes in Table 2 are for a state space in the .bcg format, except the *comb network* entries which represent a state space in the .aut format. Minimised state spaces are always in the .bcg format. In some cases, the .bcg version has fewer states for the same state space than the original .aut version.

- In Table 3, the full state space size is listed for each model. When using the actl library, the full state space is explored, even when errors are found. When using the walk\_actl library, the verification stops after the construction of the first diagnostic trace. We do not know how many states and transitions were explored by walk\_actl to construct the diagnostic traces.

- The Promela models for 2 DCM Managers are more efficient than the ones with 3 DCM Managers in the sense that they use the datatype bit instead of byte for the Id parameter in the general process DCM\_Manager.

- With Spin we first tried to explore the whole state space. Whenever an error was found, we reran the verification with a smaller search depth (option '-m' at run time) to see if a smaller error trail could be found. In this way we found the trails reported in Table 1, which are the shortest trails we could find. Sometimes the search for a shorter trail involves the exploration or more states and transitions, due to the order in which the depth-first search is performed.