A Timed Verification of the IEEE 1394 Leader Election Protocol

J.M.T. Romijn

Software Engineering (SEN)

SEN-R9919 August 31, 1999

Report SEN-R9919 ISSN 1386-369X

CWI P.O. Box 94079 1090 GB Amsterdam The Netherlands

CWI is the National Research Institute for Mathematics and Computer Science. CWI is part of the Stichting Mathematisch Centrum (SMC), the Dutch foundation for promotion of mathematics and computer science and their applications.

SMC is sponsored by the Netherlands Organization for Scientific Research (NWO). CWI is a member of ERCIM, the European Research Consortium for Informatics and Mathematics.

Copyright © Stichting Mathematisch Centrum P.O. Box 94079, 1090 GB Amsterdam (NL) Kruislaan 413, 1098 SJ Amsterdam (NL) Telephone +31 20 592 9333 Telefax +31 20 592 4199

## A Timed Verification of the IEEE 1394 Leader Election Protocol \*

Judi Romijn

CWI

P.O. Box 94079, 1090 GB Amsterdam, The Netherlands

judi@cwi.nl

#### **ABSTRACT**

The IEEE 1394 architecture standard defines a high performance serial multimedia bus that allows several components in a network to communicate with each other at high speed. In the physical layer of the architecture, a leader election protocol is used to find a spanning tree with a unique root in the network topology. If there is a cycle in the network, the protocol treats this as an error situation. This paper presents a formal model of the leader election protocol in the language IOA as well as a correctness proof. The verification shows that under certain timing restrictions the protocol behaves correct. The timing constants proposed in the IEEE 1394 standard documentation obey the requirements found in this proof.

1991 Mathematics Subject Classification: 68M10, 68Q05, 68Q45, 68Q60, 94C15

1991 ACM Computing Classification System: F.1.1, F.4.1, G.2.2

Keywords and Phrases: protocol verification, I/O automata, safety, liveness, real time, refinement, simulation Note: The results reported in this paper have been obtained as part of the research project "Specification, Testing and Verification of Software for Technical Applications", carried out by the Stichting Mathematisch Centrum for Philips Research Laboratories under Contract RWC-061-PS-950006-ps.

The author's current affiliation is: Computing Science Institute, University of Nijmegen, P.O. Box 9010, 6500 GL Nijmegen, The Netherlands.

### 1 Introduction

The IEEE 1394-1995 serial bus standard [10] defines an architecture that allows several components to communicate at very high speed. Originally, the architecture was designed by Apple (FireWire). Currently, more than 70 companies are involved in the standardisation effort. Although the IEEE 1394-1995 standard has been finalised, the architecture is still being refined and adapted. Part of this ongoing work is reflected in the IEEE P1394a standard proposal document [11], which is intended to be a supplement to IEEE 1394-1995. In this paper, 1394 will refer to IEEE 1394-1995 unless otherwise stated.

The IEEE 1394 standard allows several components to be connected either with cables and IEEE 1394 chips (cable environment), or with an IEEE 1394 backplane in one physical device (backplane environment). We restrict our attention to the cable environment situation, and refer to the whole of components, cables, etc. as *the network*.

Like in the OSI model, the IEEE 1394 architecture has several layers of which the physical layer is the lowest. This layer takes care of the actual communication on the bus, which happens

<sup>\*</sup> A short version of this report appeared in S. Gnesi and D. Latella, editors, *Proceedings of the Fourth International Workshop on Formal Methods for Industrial Critical Systems (FMICS'99)*, pages 3–29, May 1999.

1. Introduction 2

by sending signals on a wire by asserting voltages. The physical layer is responsible for the knowledge that a component has of the network topology and of components present, and for issues such as timing of asynchronous and synchronous communication and arbitration for use of the bus. These tasks are taken care of in several phases. The first phase in the physical layer is the bus reset phase, which is entered whenever a component is powered up, when the network topology changes or an error is discovered, or on request of higher layers in the architecture. After completion of the bus reset phase, the tree identify phase starts. In the three identify phase the network topology is determined by spanning a tree in the network. The root of the tree will act as the bus master. After the tree identify phase, the self identify phase follows in which all components inform the rest of the network of their capabilities and get a unique ID. Finally, in the normal operation phase, the arbitration for and actual use of the bus by higher layers and applications takes place.

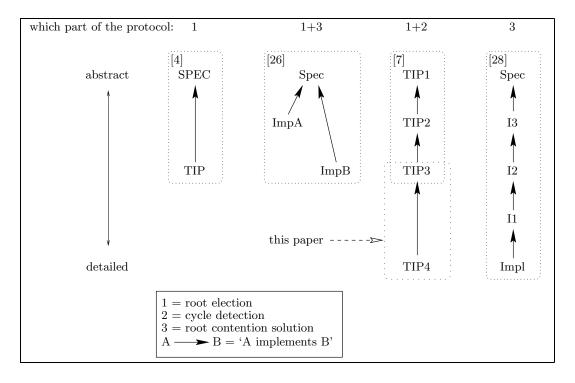

In this paper we study the tree identify phase in the physical layer. The components employ a leader election protocol to span a tree in the network, with the root acting as the leader. A side effect of the protocol is that it detects whether there is a cycle in the network, and if so, does not terminate with a leader but halts in the initial phase of the protocol and issues error messages. Our intention is to prove that an abstraction of the protocol, which is as close to the description in the IEEE 1394 documents [10, 11] as possible, works correct. There already are some correctness proofs for other abstractions of this protocol [4, 26, 7, 28]. We reuse part of this work for proving the correctness of our model of the protocol. This is done by establishing an implementation relation between the most detailed model from [7] and our more detailed model of the protocol. In this way, our verification adds to a stepwise refinement of IEEE 1394 in which more detail is added to models in each step.

The verification is carried out by establishing timed trace inclusion between timed I/O automata through a timed refinement [16, 17, 19]. The I/O automata are presented in the IOA language [5]. We reuse an untimed I/O automaton from [7] to which we add a harmless time-passage action to turn it into a timed I/O automaton and use timed refinements as presented in [19]. As mentioned in [19], we could equally well establish an untimed refinement between the timed I/O automata, so timed trace inclusion follows if the time-passage action is visible in both models. Some related work that is interesting in the timed vs. untimed respect is the work presented in [23], which discusses safety and failure refinements between timed and untimed CSP models [3]. Some results are presented for failure refinements between communicating processes, which may be useful in the I/O automata setting.

The proofs show that under the assumptions made, the behaviour of the models is correct when we use the timing constants proposed in IEEE 1394-1195 and IEEE P1394a. It still remains to be seen whether further refinement of the models preserves the correctness.

This paper is organized as follows. Section 2 explains the IEEE 1394 tree identify, discusses related verifications and presents our abstraction. Section 3 introduces our I/O automata models of the tree identify protocol and shortly discusses the IOA language. Section 4 is an intermezzo about network topologies, in which general results are derived that we need in the verification. Section 5 presents the formal verification of the protocol. In Section 6 we sum up the conclusions that can be drawn from this exercise. We have added Appendix A to give the basic definition and principles used in this verification. Here we also present a new result for reusing invariants in a stepwise refinement proof, which is used in Section 5, as well as new sufficient conditions for feasibility, which are used in Section 5.3.

Note that to improve readibility, we often use Lamport's list notation [13] for conjunction or disjunction in formulas.

# 2 The protocol

In this section, the IEEE 1394 tree identify phase is described, other verifications of this protocol are discussed, and our our abstraction is introduced. The IOA models are presented in Section 3. The tree identify phase has already been described in several articles. The following text and pictures borrow from [4].

### 2.1 The IEEE 1394 tree identify phase

We refer to the components connected to 1394 bus as devices. Each device has a number of ports which are used for bidirectional connections to other devices. Each port has at most one connection. The device at the other side of the connection is called the peer device. The tree identify phase follows on completion of the bus reset phase, which is started as soon as a total reset of the network is demanded. This can occur on request of applications, or because the network configuration has changed or an error situation has been detected. The bus reset phase clears all topology information except local information on a device, namely which ports have connections. During the tree identify phase a spanning tree is constructed in the network. After the tree identify phase completes, the tree structure will be used in the normal bus operation. An example of a network topology at the start of the tree identify phase is presented in Figure 1.

Figure 1: Initial network topology

Figure 2: Intermediate configuration

Informally, the basic idea of the protocol is as follows: each device starts in the initial phase, in which it may receive a "parent request" on from a peer device on one of its ports. The receiving device then sends an acknowledgement message to the peer device and adds the port to its collection of children. A peer device which is connected to the child port, is then considered to be a child in the tree structure. See Figure 2. When a device is in the initial phase and it has no more than one port left on which no communication has taken place yet, it can send a parent request on that port and leave the initial phase. It is obvious that leaf devices (i.e. devices with one connected port) have exactly one such port at the start of the protocol, so they can send their parent request and leave the initial phase immediately. In this manner, a tree is constructed that grows from the leaves inward, until all ports of one device are children, and that device is the *root* of the tree. See Figure 4.

It is possible that two devices end up asking each other to be the parent. This situation is called "root contention". The devices both signal the reception of a parent request on a port on which they already sent a parent request, and turn to a symmetry breaking protocol in which random bits are used. See Figure 3. This root contention protocol has been formally specified and verified in [28].

When a cycle is present in the network, all the devices that are on such a cycle will not get a parent request from their peers on the cycle. So they will have more than one port on which no parent request was received, and can therefore not send a parent request themselves or leave

Figure 3: Two contending devices

Figure 4: Final spanning tree

the initial phase. Also devices that are not on a cycle, but are wedged between two or more cycles will not get a parent request on at least two ports, and will not send a parent request themselves or leave the initial phase. Such a situation is solved by a timer which is started at the start of the tree identify phase, and which is supposed to expire only in the situation of a cycle in the network. When there is a cycle in the network, a root should not be elected, since the operation of the bus in the following phases relies on the topology being a tree structure.

A device may influence its own chances at becoming root by waiting for some time before sending the parent request, even if it is already possible to proceed. A device will only do so if it has the flag force\_root set to true.

Devices may enter the tree identify phase at different times. This is due to the difference in the moments at which different devices signal that the bus reset phase (preceding the tree identify phase) should be entered.

### 2.2 Other verifications of the protocol

Parts of the IEEE 1394 architecture have been formally specified and/or verified in several articles [14, 12, 4, 7, 27, 26, 28]. Of these, [14, 12, 27] focus on the link layer. The articles [4, 26, 7, 28] study the tree identify phase of the physical layer, like this paper does. In Figure 5 we give an overview of the results of these articles, and their relation to the research presented in this paper. The results of the different articles are in the dashed boxes. The names of the formal models are listed, arrows between these indicate a (proved) implementation relation. The vertical position of a model name indicates the level of abstraction of that model with respect to the IEEE 1394 documentation. Very abstract models do not consider implementation details such as timing, signals etc. The most detailed models incorporate more detail from the IEEE 1394 documentation. In the picture, we have given some models the same vertical position to indicate that they have a comparable degree of detail. We now explain the results of each article in short.

Devillers, Griffioen, Romijn and Vaandrager [4] have shown that the election in the tree identify phase works correct, under the assumption that there are no cycles in the network, that the network topology is fixed throughout the protocol, that a root contention situation is solved in one atomic step, and that no device tries to become root by having the corresponding force\_root flag set to true. The models are at a high level of abstraction: there is no timing and communication is modelled with finite queues. The models are I/O automata [16, 17] presented in a precondition/effect style. The proofs use invariants and simulation techniques from [18]. The proofs have been checked with the theorem prover PVS [22].

Shankland and van der Zwaag [26] have also shown that the election in the tree identify phase works correct, under the assumption that there are no cycles in the network, that the network topology is fixed throughout the protocol, and that no device tries to become root by having

Figure 5: An overview of research on the IEEE 1394 tree identify phase

the corresponding force\_root flag set to true. The models are at a high level of abstraction: there is no timing and communication is modelled with finite queues. The models are presented in  $\mu$ CRL [8], a process algebra language with data. The proofs use invariants and the cones and foci method from [9]. Note that the paper gives no proof that the root contention protocol actually terminates within bounded time, since for the verification it is enough to show that it can terminate.

Griffioen and Vaandrager [7] have shown that the election in the tree identify phase works correct, under the assumption that the network topology is fixed throughout the protocol, that a root contention situation is solved in one atomic step, and that no device tries to become root by having the corresponding force\_root flag set to true. The models are at a high level of abstraction: there is no timing and communication is modelled with finite queues. The models are I/O automata [16, 17] presented in the IOA language [5]. The paper introduces a new simulation proof technique, called normed simulations. The proofs use invariants and the proposed simulation technique. The proofs have been checked with the theorem prover PVS [22]. Note that cycle detection is done with a predicate that takes the structure of the whole network into account, and does not use timing information, as in IEEE 1394. The predicate used implies that nodes that are part of a cycle will detect this with an error message. In IEEE 1394 (and in the models presented in this paper), the error situation is also detected by nodes that are not part of a cycle themselves, but wedged in between of two cycles.

Stoelinga and Vaandrager [28] have shown that the root contention solving protocol in the tree identify phase works correct under the assumption that the network topology is fixed throughout the protocol. The models are at an intermediate level of abstraction: on the one hand timers and probabilities are used, but on the other hand communication is modelled with finite queues. The models are probabilistic timed I/O automata [24, 25] presented in the IOA language [5].

The paper introduces two simulation proof techniques, which are special cases of the simulation techniques in [24, 25]. The proofs use invariants and the proposed simulation techniques.

The model of the protocol that is presented in [4] is essentially the same as one of the I/O automata examples in the book *Distributed Algorithms* by Lynch [15]. A correctness proof of this protocol is not given in [15]. The models that either include cycle detection or the root contention protocol are can be considered refinements of the protocol in [15].

#### 2.3 This verification

As can be seen in Figure 5, this paper aims to give an implementation relation between the most detailed model from [7] and a more detailed model. In this way, our verification adds to a layered verification of IEEE 1394 in which models are refined, that is, more and more detail is added in each step. In order to keep our proof obligations manageable, we do not add too much detail, and hence our model has an intermediate degree of detail with respect to IEEE 1394.

The verification is carried out by establishing trace inclusion between timed I/O automata through a refinement [16, 17, 19]. The I/O automata are presented in the IOA language [5].

The most detailed model of [7] is an untimed model. This means that the cycle detection is done with a predicate that takes the structure of the whole network into account. In this verification, we want to establish that cycle detection based on the timing in IEEE 1394 works correct. In order to do this, we add timers to the model which expire when the leader election takes too much time. We also add timing information to the messages sent, in order to model the delay in communication in IEEE 1394. As argued above, this paper uses a different predicate for cycle detection than the one used in [7], in order to conform to the error behaviour of IEEE 1394. As in [7] we assume that the network topology is fixed throughout the protocol, that a root contention situation is solved in one atomic step that no device has the force\_root flag set to true, and that communication can be modelled with finite queues.

Since our aim is to show that whenever timers in the model expire, there is indeed a cycle in the network, and that the timers will expire in case of a cycle in the network, we are trying to show that the timers do not expire too soon or too late. In our proofs we use invariants that express worst case scenarios in terms of delay. So we are actually performing a worst case analysis on the timing proposed in IEEE 1394. In this way, we establish a relation between the parameters of the protocol in terms of minimal and maximal values.

We expect that in a next refinement step it is possible to include the result from [28], to get closer to the IEEE 1394 behaviour without much effort. The next refinement step could then be to add a force\_root flag to the model, thus expressing that devices behave a little different to increase their chances at leadership. In order to obtain a correctness statement about IEEE 1394 with all its detail, it still has to be shown that modelling the IEEE 1394 communication of voltages on wires by messages and finite queues is correct. We expect that in this situation, we will not just have a judgement on correctness, but we will also be able to say how the timing constants in IEEE 1394 could/should be adjusted.

**Our assumptions** As a specification of the desired behaviour, we have taken the most detailed model TIP3 from [7]. In [7] it is shown that the behaviour of TIP3 meets the requirements for the tree identify phase.

TIP3 is a very abstract model of the tree identify phase, in the sense that it abstracts from a lot of details. We introduce a model TIP4, which is more detailed than TIP3, and prove that it is a refinement of TIP3. In this way, the correctness of the behaviour of TIP4 can be derived

from the correctness of the behaviour of TIP3.

Our justification for still leaving out many implementation details that may affect the correctness of the protocol, is that we intend to reuse as much as possible of the proofs already established. This can only be done in a manageable way if we do not add too many details at once. As it is, the proofs for our verification are already quite lengthy and involved. See also Section 6 for a discussion of our results.

The abstractions have been chosen as follows.

- In TIP3, it is assumed that the devices signal a cycle by merely checking the network topology. In TIP4, the devices use a timer, which conforms to IEEE 1394.

- In both TIP3 and TIP4, communication between devices is modelled by sending messages on queues. In a IEEE 1394 network, the devices communicate by asserting signals (defined in terms of voltages) on wires for a certain time.

- In both TIP3 and TIP4, it is assumed that no device has the force\_root flag set to true.

- In both TIP3 and TIP4, the network is assumed to be connected and to be fixed throughout the protocol. There may be cycles in the topology.

- In both TIP3 and TIP4, the root contention situation is solved in one atomic step, as opposed to the IEEE 1394 protocol which involves picking random bits, and which repeats until the symmetry is broken. Note that the root contention protocol has been formally specified and proved correct in [28].

- In both TIP3 and TIP4, all devices enter the tree identify phase at the same time.

- In TIP3, no timing is used whatsoever. In TIP4, timing is used for determining whether the network topology contains a cycle (see above), and for determining the actual delivery time of messages. The IEEE 1394 delay between the moment of sending and reception and processing of a signal is caused by difference in clocks of the devices, the length and propagation delay of the wires, and the difference in the tree identify phase enter moment of the sending and receiving device. In TIP4, the delay of message is determined at the moment that the message is being received. This delay may vary between the bounds caused by difference in clocks of the devices, and by the length and propagation delay of the wires. Although the second factor is constant, we have modelled the choice of delay to be completely free for each receive operation. Since we are after the bounds on the timing constants in relation to the network topology with respect to detecting cycles, we are establishing the property that the cycle detection timer will not expire too soon or too late. Therefore we are actually performing a worst case analysis. The worst case scenarios for IEEE 1394 and our model are the same, under the assumption that all devices enter the tree identify phase at the same moment.

### 3 IOA models

We present two models in the IOA language [5] of the tree identify protocol, namely TIP3 and TIP4. The IOA model for TIP3 comes (almost) literally from [7] and gives an abstract and untimed model of the protocol behaviour. It has been shown in [7] that this model has the desired behaviour of electing exactly one device for root if there is no cycle in the network. If

Figure 6: Signature for TIP3 and TIP4.

there is a cycle in the network, all devices that are part of this cycle will detect this and give an error message.

The IOA language The IOA language facilitates precise and readable descriptions of I/O automata [16, 17]. Since our models are timed, we have added a **time** action, according to the definition in [19].

IOA contains the basic types Bool, Nat, Int and Real with their standard operators. In addition type constructors Array, Seq (finite sequences) and Set (finite sets) are part of the language. The notation \_\_[\_] is used for array subscripting, an array with a value e in all cells is denoted by const(e). The operation \_\bullet\_\_ appends an element at the end of a sequence and the operations head and tail have the usual meaning. We assume the type Time which is the (predefined) type Real restricted to nonnegative values.

We assume the extra types Mes to represent the different message contents that may be exchanged between devices, as follows:

#### Type Mes enumeration of parent, ack

In Section 4 we give several definitions and operations that concern network topologies. Given a network  $N = \langle D, P, \text{dev}, \text{peer} \rangle$ , we assume the types Dev = D and Port = P and all operations as defined in Section 4.

The TIP models The signature part for both models is shown in Figure 6. The connected network  $N = \langle D, P, \text{dev}, \text{peer} \rangle$  is a parameter for both models. In addition, the constants MinDelay, MaxDelay, MinLpdtime, and MaxLpdtime are parameters for TIP4. We assume MinDelay  $\leq$  MaxDelay and MinLpdtime  $\leq$  MaxLpdtime.

The IOA description of TIP3 is shown in Figure 7. The action definitions are almost equal to those of TIP4, so we refer to the explanation below. The model TIP3 comes (almost) literally from [7]. The first change is the addition of the time action, whose precondition is true, and whose effect is empty. The second change is the use of the oncycle predicate, which recognizes not just devices that are on an ordinary cycle, but also devices that are on a path between two cycles (see Section 4). Our verification shows that these devices also detect a cycle in the protocol and give an error message (see property  $I_{12}$  in Definition 5.1, Section 5.1).

The IOA description of TIP4 is shown in Figure 8. The model TIP4 is a proper timed IOA model: there is a state variable time which is used as a global clock, and per message queue

```

automaton TIP3

states

child: Set[Port] := \{\}

mq: Array[Port,Seq[Mes]] := const({})

init: Array[Dev,Bool] := const(true)

rc, root, lpd: Array[Dev,Bool] := const(false)

transitions

internal childrenknown(d)

pre init[d] \( \) size(ports(d)-child) < 1</pre>

eff init[d] := false;

for p in ports(d) do if p \in child

then mq[p] := mq[p] \vdash ack

else mq[p] := mq[p] \vdash parent fi od

internal addchild(d,p) where d = dev(p)

pre init[d] / head(mq[peer(p)]) = parent

eff child := insert(p, child);

mq[peer(p)] := tail(mq[peer(p)])

internal receivemes(d,p,m) where d = dev(p)

pre \neg init[d] \land ports(d)-child = \{p\} \land head(mq[peer(p)]) = m

eff if m = parent then rc[d] := true fi;

mq[peer(p)] := tail(mq[peer(p)])

internal solverootcontent(d,p) where d = dev(p)

pre rc[d] \( \text{rc[dev(peer(p))]}\)

eff child := insert(p,child);

rc[d] := false;

rc[dev(peer(p))] := false

output root(d)

\operatorname{pre} \neg \operatorname{init}[d] \land \neg \operatorname{root}[d] \land \operatorname{ports}(d) \subseteq \operatorname{child}

eff root[d] := true

output loopdetect(d)

pre oncycle(d) \lambda \square lpd[d]

eff lpd[d] := true

time \delta where \delta > 0

pre true

eff

```

Figure 7: Automaton TIP3.

```

automaton TIP4

states

child: Set[Port] := {}

mq: Array[Port,Seq[Mes]] := const({})

delay: Array[Port,Time] := const(0)

init: Array[Dev,Bool] := const(true)

rc, root, lpd: Array[Dev,Bool] := const(false)

time: Time := 0

transitions

internal childrenknown(d)

pre init[d] \( \) size(ports(d)-child) \( \le 1 \)

eff init[d] := false;

for p in ports(d) do delay[p] := 0;

\mathbf{if} \ \mathtt{p} \in \mathtt{child}

then mq[p] := mq[p] \vdash ack

else mq[p] := mq[p] \vdash parent fi od

internal addchild(d,p) where d = dev(p)

pre init[d] \( \lambda\) head(mq[peer(p)])=parent \( \lambda\) delay[peer(p)] \( \geq \) Mindelay

eff child := insert(p, child); mq[peer(p)] := tail(mq[peer(p)])

internal receivemes(d,p,m) where d = dev(p)

pre \land \neg init[d] \land ports(d)-child = \{p\}

\land head(mq[peer(p)])=m \land delay[peer(p)] \ge Mindelay

eff if m = parent then rc[d] := true fi;

mq[peer(p)] := tail(mq[peer(p)])

internal solverootcontent(d,p) where d = dev(p)

pre rc[d] \( \) rc[dev(peer(p))]

eff child := insert(p,child);

rc[d] := false; rc[dev(peer(p))] := false

output root(d)

pre \neg init[d] \land \neg root[d] \land ports(d) \subseteq child

eff root[d] := true

output loopdetect(d)

pre init[d] \land \neg lpd[d] \land time \ge MinLpdtime

eff lpd[d] := true

time \delta where \delta > 0

pre \forall d,p:

\land \neg pre(childrenknown(d)) \land \neg pre(root(d))

\land if init[d] \land \neg lpd[d] then time+\delta \le MaxLpdtime fi

\land if mq[p] \neq {} then delay(mq[p])+\delta \leq MaxDelay fi

\mathbf{eff} \ \mathsf{time} := \mathsf{time} + \delta

for p in Port do delay[p] := delay[p]+\delta od

```

Figure 8: Automaton TIP4.

there is a variable delay that is reset for each message sent on the corresponding queue. A message is available at least after MinDelay time units have passed or ultimately after MaxDelay time units have passed. The condition for detecting a cycle in the network also depends on time, and not (as in TIP3) on the predicate oncycle which is based on the structure of the network. It is our goal to show that cycle detection will occur if and only if there really is a cycle present in the network.

We now give a short explanation of each action of TIP4. Whether a device is in the initial phase is reflected in the state variable init. When init is true, only actions addchild and childrenknown can be enabled. With addchild a parent request may be received (if the value of delay indicates that the parent request is available) and the corresponding port is added to the collection of children. The action childrenknown marks the end of the init phase. It can only be performed when there is at most one port left which is not a child port, and when it is performed, an acknowledgement is sent to all peer devices that are connected to a child port and a parent request is sent to the peer device connected to the port that is not a child, if any. If a device is on a cycle, then it does not ever reach the state in which childrenknown is enabled, because two of its ports are connected to peer devices which are also on a cycle. In this situation, the action loopdetect should be performed. In TIP3, the cycle is detected with the oncycle predicate. In TIP4, a timer signals that the device stays in the init phase too long, and therefore must be on a cycle. As soon as a device has left the init phase, it must wait for a message on the one remaining port that is not a child. If there is no such port, then the device is the root of the tree, and can perform the root action. If there is such a port, then the action receivemes can be performed as soon as the message is available. The expected message is an acknowledgement, after which the contribution of the device to the leader election is over. If an unexpected parent request is received, then the device is in root contention with the peer device that sent the parent request. The peer device has received or will receive the parent request that was sent earlier, and thus has signalled or will signal the root contention. As soon as both devices have signalled root contention, the action solverootcontent can be performed to break the symmetry and add one of the two ports involved to the child collection. The device whose port is added to child can then perform the root action. The time action signals the passing of time, by increasing the value of time. Time passage may not occur if there are other actions that cannot be delayed any further. Actions childrenknown and root are urgent, which means that they should happen at the first moment when they are enabled. Actions addchild and receivemes are also urgent, but they are enabled only when a message becomes available. Since the message is available only when the value of delay is in the interval [MinDelay, MaxDelay], we require that the value of delay does not pass beyond the right-hand border of this interval. The action loopdetect depends on the the value of time and can happen anywhere in the interval [MinLpdtime, MaxLpdtime], so we require that time does not pass beyond MaxLpdtime. The only action that is not mentioned in the precondition of the time action, is solverootcontent. The reason for this is that in the IEEE 1394 documentation, there is a small sub-protocol with timers that is used to break the symmetry, instead of the one action that represents this sub-protocol in TIP4. Since this sub-protocol is not guaranteed to end in finite time (due to randomly drawn bits), we cannot say at what time the action solverootcontent will take place. Hence we have put not requirement on the time action for solverootcontent. The root contention solving protocol is discussed and proved correct in [28].

## 4 Network preliminaries

This section gives some definitions and properties of network topologies which are needed in the verification.

#### 4.1 Networks

**Definition 4.1** A *network* is a quintuple  $\langle D, P, \text{dev}, \text{peer} \rangle$ , where

- *D* is a non-empty set of devices.

- P is a set of ports.

- $\operatorname{dev}: P \to D$ .

- peer:  $P \to P$  with for all p: peer(peer(p)) = p and  $p \neq peer(<math>p$ ).

For  $d \in D$ , we define the abbreviation  $ports(d) = \{p \in P | dev(p) = d\}$ . Given D' and  $d \in D'$ , the predicate leaf(D', d) holds iff  $\forall p_1, p_2 \in ports(d) : dev(peer(p_1)) \in D' \land dev(peer(p_2)) \in D' \rightarrow p_1 = p_2$ .

The network consists of a collection of devices, each of which has a set of ports. Each port is connected to one other port with a cable, which is captured by the function peer. Each port has a connection and no port is connected to itself. The cable connection itself is referred to as a cable hop. Since for each  $p \in P$ , dev(p) is defined, it follows that  $P = \bigcup_{d \in D} ports(d)$ .

Throughout this paper, we fix a network  $N = \langle D, P, \text{dev}, \text{peer} \rangle$  and let variables  $p, p', p'', p_0, \ldots$  range over ports in P, and  $d, d', d_0, \ldots$  over devices in D.

## 4.2 Paths, cycles

The following definitions and lemmas are necessary to identify paths, cycles, etc. in the network.

**Definition 4.2** A path  $\pi$  is a non-empty sequence of ports  $\pi = p_0 p_1 \dots p_n$ , such that:

- n is odd

- $p_0 \neq p_n$

- for all i > 0, if i is odd then  $p_{i-1} = peer(p_i)$  else  $dev(p_{i-1}) = dev(p_i)$

We denote the first and last port of  $\pi$  with  $first(\pi) = p_0$  and  $last(\pi) = p_n$ . We denote the length of  $\pi$  with  $length(\pi) = (n+1)/2$ . We denote the path obtained by reversing  $\pi$  with  $reverse(\pi) = p_n \dots p_0$ .

Path  $\pi$  is a path from  $d_1$  to  $d_2$  if  $\operatorname{dev}(\operatorname{first}(\pi)) = d_1$  and  $\operatorname{dev}(\operatorname{last}(\pi)) = d_2$ . We say that a device d is on  $\pi$  iff there is a port p in  $\pi$  such that  $d = \operatorname{dev}(p)$ . A cycle is a path  $\pi = p_0 \dots p_n$  such that  $\operatorname{dev}(p_0) = \operatorname{dev}(p_n)$ .

The predicate oncycle(p) is true iff there is a cycle such that p is on it. The predicate oncycle(d) is true iff there is a port  $p \in ports(d)$ , such that oncycle(p) holds.

A path reflects a walk through the network by the concatenation of cable hops, in which a  $p_1p_2$  cable hop may not be followed immediately by the reverse hop  $p_2p_1$ . The length of a path is the number of cable hops included in that path. A cycle may include a path  $\pi$  which is wedged in between smaller cycles  $\rho$  and  $\tau$ , resulting in the shape of a pair of glasses:  $\rho\pi\tau$ reverse $(\pi)$ .

Ports that are part of a cycle (of whatever shape) remain inactive during the protocol, as we will show later.

**Lemma 4.3** If  $\pi = p_0 p_1 p_2 \dots p_n$  is a cycle, then  $p_2 \dots p_n p_0 p_1$  and  $\text{reverse}(\pi)$  are also cycles.

**Lemma 4.4**  $oncycle(p) \rightarrow oncycle(peer(p))$

**Lemma 4.5** oncycle $(p) \rightarrow \text{size}(\{p'|p' \in \text{ports}(\text{dev}(p)) \land \text{oncycle}(p')\}) \ge 2$

**Proof** Let  $\pi = p_0 p_1 \dots p_n$  be a cycle such that  $p = p_i$ .

If i = 0, then by definition of a cycle,  $\operatorname{dev}(p_n) = \operatorname{dev}(p)$ , and by definition of a path,  $p_n \neq p$ . If i is even and i > 0, then by definition of a path,  $\operatorname{dev}(p_{i-1}) - \operatorname{dev}(p)$  and  $p_{i-1} \neq p$ . If i = n, then by definition of a cycle,  $\operatorname{dev}(p_0) = \operatorname{dev}(p)$ , and by definition of a path,  $p_0 \neq p$ . If i is odd and i < n, then by definition of a path,  $\operatorname{dev}(p_{i+1}) - \operatorname{dev}(p)$  and  $p_{i+1} \neq p$ .

**Lemma 4.6** Let  $N = \langle D, P, \text{dev}, \text{peer} \rangle$  be a connected network, and  $d_1, d_2 \in D$ . If  $\text{oncycle}(d_1)$ ,  $\text{oncycle}(d_2)$ , and  $\pi$  is a path from  $d_1$  to  $d_2$ , then for each  $p \in \pi$ : oncycle(p)

**Proof** Let  $\rho$  be a cycle such that  $d_1$  is on it. Let  $\tau$  be a cycle such that  $d_2$  is on it. We will show for each port p in  $\pi$  that oncycle(p), as follows.

Let  $\pi = p_0 \dots p_n$ . If  $p_i$  is in  $\rho$  or  $\tau$ , then  $\mathsf{oncycle}(p_i)$ . We take a fragment  $\pi' = p_i \dots p_j$  from  $\pi$  such that i > 0 implies that  $p_{i-1}$  in  $\rho$  or in  $\tau$ , and j < n implies that  $p_{j+1}$  in  $\rho$  or in  $\tau$ , and for each port p on  $\pi'$ , p is not on  $\rho$  and not on  $\tau$ . If we can construct a cycle such that the fragment  $\pi'$  is part of it, we are done.

Note that by definition,  $dev(p_i)$  is on  $\rho$  or on  $\tau$ , and  $dev(p_j)$  is on  $\rho$  or on  $\tau$ .

In the following case distinction we leave out all cases which are symmetric to a case proved earlier.

- 1.  $p_i = p_j$ . We assume w.l.o.g. that  $dev(p_i)$  is on  $\rho$ . Let  $\rho = \rho_1 \rho_2$  such that  $dev(p_i) = dev(last(\rho_1)) = dev(first(\rho_2))$  and  $length(\rho_1)$  is even. By assumption,  $last(\rho_1) \neq p_i = p_j \neq first(\rho_2)$ . We construct the path  $\rho_2 \rho_1 \pi'$  and see that it is a cycle.

- 2.  $p_i \neq p_j$ . We assume w.l.o.g. that  $dev(p_i)$  is on  $\rho$  and  $dev(p_j)$  is on  $\tau$ . Let  $\rho = \rho_1 \rho_2$  such that  $dev(p_i) = dev(last(\rho_1)) = dev(first(\rho_2))$  and  $length(\rho_1)$  is even. Let  $\tau = \tau_1 \tau_2$  such that  $dev(p_j) = dev(last(\tau_1)) = dev(first(\tau_2))$  and  $length(\tau_1)$  is even. By assumption,  $last(\rho_1) \neq p_i \neq first(\rho_2)$  and  $last(\tau_1) \neq p_j \neq first(\tau_2)$ . We construct the path  $\rho_2 \rho_1 \pi' \tau_2 \tau_1 reverse(\pi')$  and see that it is a cycle.

$\boxtimes$

#### 4.3 Connected networks

The following definitions and lemmas are necessary to identify the distance of devices in the network to the edge of the network, that is, how many times we have to take all the leaf devices away before a device becomes a leaf in the remaining set. The distance measure defined here will be used in the protocol to quantify the worst-case time that it takes for a device to complete its part in the protocol.

**Definition 4.7** N is connected if for each two devices  $d, d' \in D$  there is a path from d to d'. If N is connected, we denote the maximum length of the shortest path in N between any two

devices by MaxHop =  $\max(\{n|d_1, d_2 \in D \land n = \min(\{\text{length}(\pi)|\pi \text{ is path from } d_1 \text{ to } d_2\})\})$ . The function Steps is defined by the following equation:

$$\begin{split} \mathtt{Steps}(D',d) &= \left\{ \begin{array}{ll} 0 & \textit{if} \ \mathtt{leaf}(D',d) \ \textit{or} \ \mathtt{oncycle}(d) \\ 1 + \mathtt{Steps}(D'',d) & \textit{otherwise} \end{array} \right. \\ \textit{where} \ D'' &= D' - \{d' \in D' | \mathtt{leaf}(D',d') \} \end{split}$$

We abbreviate Steps(d) = Steps(D, d).

The function Shrink is defined by the following equation:

$$\begin{split} \operatorname{Shrink}(D',n') &= \left\{ \begin{array}{ll} D' & & \textit{if } n' = 0 \\ \operatorname{Shrink}(D'',n'-1) & & \textit{otherwise} \end{array} \right. \\ \textit{where } D'' &= D' - \left\{ d' \in D' | \operatorname{leaf}(D',d') \right\} \end{split}$$

We abbreviate Shrink(n) = Shrink(D, n).

The value MaxHop, which is an upper bound to the minimum number of cable hops between any two devices, is used in the IEEE documentation as a restriction on the networks on which the protocol is to operate.

The function Steps gives the one but greatest distance between a device and a leaf in the network. This number is determined by the number of steps it takes for such a device to become a leaf, when in each step all leafs are removed. For a device that is part of a cycle, the value of Steps has no meaning and will not be used.

The function Shrink gives the set of devices that remains when in each step the leaf devices are removed and this is repeated for the indicated number of times, starting with the given set. The correspondence between Steps and Shrink is obvious: if Steps(d) = n then leaf(Shrink(n), d) holds and if  $Steps(d) \ge n$  then  $d \in Shrink(n)$ .

In the remainder of this paper, we assume that N is connected.

**Lemma 4.8** Let  $d \in D$  such that  $\neg oncycle(d)$ .

If  $\mathsf{Steps}(d) = n \text{ then } \mathsf{size}(\{p' \in \mathsf{ports}(d) | \mathsf{oncycle}(\mathsf{dev}(\mathsf{peer}(p')) \lor \mathsf{Steps}(\mathsf{dev}(\mathsf{peer}(p'))) \ge n\}) \le 1.$

**Proof** By contradiction. Assume  $\neg \mathsf{oncycle}(d)$  and  $\mathsf{Steps}(d) = n$ . Let  $p, p' \in \mathsf{ports}(d)$  such that  $p \neq p'$  and  $\mathsf{oncycle}(\mathsf{dev}(\mathsf{peer}(p)) \vee \mathsf{Steps}(\mathsf{dev}(\mathsf{peer}(p))) \geq n$  and  $\mathsf{oncycle}(\mathsf{dev}(\mathsf{peer}(p')) \vee \mathsf{Steps}(\mathsf{dev}(\mathsf{peer}(p'))) \geq n$ . Since  $\mathsf{Steps}(d) = n$ , either  $\mathsf{oncycle}(d)$  or  $\mathsf{leaf}(\mathsf{Shrink}(n), d)$ . Since we assumed  $\neg \mathsf{oncycle}(d)$ , apparently  $\mathsf{leaf}(\mathsf{Shrink}(n), d)$ . By our assumption  $\mathsf{dev}(\mathsf{peer}(p))$  and  $\mathsf{dev}(\mathsf{peer}(p'))$  are both in  $\mathsf{Shrink}(n)$ . But  $p \neq p'$ , which contradicts  $\mathsf{leaf}(\mathsf{Shrink}(n), d)$ . We conclude that  $\mathsf{size}(\{p' \in \mathsf{ports}(d) | \mathsf{oncycle}(\mathsf{dev}(\mathsf{peer}(p')) \vee \mathsf{Steps}(\mathsf{dev}(\mathsf{peer}(p'))) \geq n\}) \leq 1$ .  $\boxtimes$

**Lemma 4.9** For each  $d \in D$

$$\mathtt{Steps}(d) \leq \left\{ \begin{array}{ll} \lfloor \mathtt{MaxHop}/2 \rfloor & \quad \textit{if} \ \forall d' \in D : \neg \mathtt{oncycle}(d') \\ \mathtt{max}(0,\mathtt{MaxHop}-1) & \quad \textit{otherwise} \end{array} \right.$$

**Proof** By contradiction.

1. Suppose  $\forall d \in D : \neg \mathsf{oncycle}(d)$ . Suppose  $\mathsf{Steps}(d) = m > \lfloor n/2 \rfloor$ . We show that we can construct a shortest path  $\pi$  with  $\mathsf{length}(\pi) > n$ , by starting with d and extending the path in each step with one cable hop

in two directions. We use induction on  $n' \in \{1, \ldots, m\}$  in the following hypothesis: There is a path  $p_0 \ldots p_{4n'-1}$  with  $\operatorname{Steps}(\operatorname{dev}(p_0)) \geq m-n'$  and  $\operatorname{Steps}(\operatorname{dev}(p_{4n'-1})) \geq m-n'$  and there is no other path from  $\operatorname{dev}(p_0)$  to  $\operatorname{dev}(p_{4n'-1})$ .

- (Base step) n' = 1Since m > 0, certainly  $\neg leaf(Shrink(m-1), d)$ , and since leaf(Shrink(m), d), there must be  $p, q \in ports(d)$  such that  $p \neq q$  and dev(peer(p)) and dev(peer(q)) in Shrink(m-1). Fix p, q. Clearly,  $Steps(dev(peer(p))) \geq m-1$  and  $Steps(dev(peer(q))) \geq m-1$ . Consider peer(p)pqpeer(q). This is a path if  $peer(p) \neq peer(q)$ . Since  $\neg oncycle(d')$  for all  $d' \in D$ , we see that  $dev(peer(p)) \neq dev(peer(q))$ , so  $peer(p) \neq peer(q)$ . If was another path from dev(peer(p)) to dev(peer(q)) then this would contradict the assumption that  $\neg oncycle(d')$  for all  $d' \in D$ . We conclude that  $\pi = peer(p)pqpeer(q)$  is a path that meets the requirements.

- (Induction step)  $n' = n'' + 1 \le m$  and the hypothesis holds for n'' Let  $\pi = p_0 \dots p_{4n''-1}$  such that  $\operatorname{Steps}(\operatorname{dev}(p_0)) \ge m n''$  and  $\operatorname{Steps}(\operatorname{dev}(p_{4n''-1})) \ge m n''$  and there is no other path from  $\operatorname{dev}(p_0)$  to  $\operatorname{dev}(p_{4n''-1})$ . We abbreviate  $d_1 = \operatorname{dev}(p_0)$  and  $d_2 = \operatorname{dev}(p_{4n''-1})$  for the first and last device of  $\pi$ . Since n'' < m,  $\operatorname{Steps}(d_1) > 0$  and  $\operatorname{Steps}(d_2) > 0$ . So  $\neg \operatorname{leaf}(\operatorname{Shrink}(m n'' 1), d_1)$  and  $\neg \operatorname{leaf}(\operatorname{Shrink}(m n'' 1), d_2)$ . So there must be  $p, p' \in \operatorname{ports}(d_1)$  and  $q, q' \in \operatorname{ports}(d_2)$  such that  $p \ne p'$ ,  $q \ne q'$ , and  $\operatorname{dev}(\operatorname{peer}(p))$ ,  $\operatorname{dev}(\operatorname{peer}(p'))$  dev $(\operatorname{peer}(q))$ , and  $\operatorname{dev}(\operatorname{peer}(q'))$  in  $\operatorname{Shrink}(m n'' 1)$ . Fix p, p', q and q'. Now for  $x \in \{p, p', q, q'\}$ :  $\operatorname{Steps}(\operatorname{dev}(\operatorname{peer}(x))) \ge m n'' 1 = m (n'' + 1) = m n'$  We assume without loss of generality that  $p \ne p_0$  and  $q \ne p_{4n''-1}$ . Consider  $\operatorname{peer}(p)p\pi q\operatorname{peer}(q)$ . This is a path if  $\operatorname{peer}(p) \ne \operatorname{peer}(q)$ . Since  $\neg \operatorname{oncycle}(d')$  for any  $d' \in D$ , we see that  $\operatorname{dev}(\operatorname{peer}(p)) \ne \operatorname{dev}(\operatorname{peer}(q))$ , so  $\operatorname{peer}(p) \ne \operatorname{peer}(q)$ . If there was another path from  $\operatorname{dev}(\operatorname{peer}(p))$  to  $\operatorname{dev}(\operatorname{peer}(q))$  then this would contradict the assumption that  $\neg \operatorname{oncycle}(d')$  for all  $d' \in D$ . We conclude that  $\operatorname{peer}(p)p\pi q\operatorname{peer}(q)$  is a path that meets all the requirements for the induction step.

We conclude that there is a shortest path in the network of length 2m. Since  $m > \lfloor n/2 \rfloor$ , certainly  $2m > (2\lfloor n/2 \rfloor) + 1 \ge n$ . So 2m > n and we have a contradiction.

#### 2. Suppose $\exists d' \in D : \mathsf{oncycle}(d')$ .

Suppose  $\mathsf{Steps}(d) = m > \mathsf{max}(0, n-1)$ . Then m > 0 and by definition of  $\mathsf{Steps}$ , certainly  $\neg \mathsf{oncycle}(d)$ . We show that we can construct a path  $\pi$  with  $\mathsf{length}(\pi) > n$ , by starting with d and a neighbour of d on a cycle, and extending the path in each step with one cable hop to a neighbour which is not on a cycle. We use induction on  $n' \in \{0, \ldots, m\}$  in the following hypothesis:

There is a path  $p_0p_1 \dots p_{2n'+1}$  with  $\operatorname{oncycle}(\operatorname{dev}(p_0))$ ,  $\operatorname{Steps}(\operatorname{dev}(p_{2n'+1})) \geq m - n'$  and for all  $1 \leq i \leq 2n' + 1$ :  $\neg \operatorname{oncycle}(\operatorname{dev}(p_i))$ , and there is no shorter path from  $\operatorname{dev}(p_0)$  to  $\operatorname{dev}(p_{2n'+1})$ .

• (Base step) n' = 0Suppose there is no  $p \in \text{ports}(d)$  such that oncycle(dev(peer(p))). Since N is connected, there must be  $\pi$ , d' such that  $\pi$  is a path  $\pi = p_0 \dots p_n$  from d' to d with oncycle(d') and for each i > 0:  $\neg \text{oncycle}(\text{dev}(p_i))$ . Fix  $d', \pi$ . Since oncycle(d') and  $\neg \text{oncycle}(\text{dev}(p_1))$ , we can use Lemma 4.8 to conclude that  $\text{Steps}(\text{dev}(p_1)) > \max(\{\text{Steps}(\text{dev}(p')|p' \in \text{ports}(\text{dev}(p_1)) \land p' \neq p_1\})$ . Then it is not hard to show

(using induction and Lemma 4.8) that  $\forall i \in \{1, 3, ..., n-2\}$ :  $Steps(dev(p_i)) \geq Steps(dev(p_{i+2}))$ . Then we easily have  $\forall i \in \{1, 3, ..., n\}$ :  $Steps(dev(p_i)) \geq m$ . Since d is chosen arbitrarily with Steps(d) > n-1, any of the devices on  $\pi$  except  $dev(p_0)$  would do. So we assume without loss of generality that there is a  $p \in ports(d)$  such that oncycle(dev(peer(p))). Fix p.

We now have  $Steps(d) \ge m$ ,  $\neg oncycle(d)$ , and oncycle(dev(peer(p))). We see that peer(p)p is a path that meets the requirements, since there cannot be a shorter path from dev(peer(p)) to d.

• (Induction step)  $n' = n'' + 1 \le m$  and the hypothesis holds for n'' Let  $\pi = p_0 \dots p_{2n''+1}$  such that  $\operatorname{oncycle}(\operatorname{dev}(p_0))$ ,  $\operatorname{Steps}(\operatorname{dev}(p_{2n''+1})) \ge m - n''$  and for all  $1 \le i \le 2n'' + 1$ :  $\neg \operatorname{oncycle}(\operatorname{dev}(p_i))$ , and there is no shorter path from  $\operatorname{dev}(p_0)$  to  $\operatorname{dev}(p_{2n''+1})$ . We abbreviate  $d' = \operatorname{dev}(p_{2n''+1})$  to indicate the last device in  $\pi$ . Since n'' < m,  $\operatorname{Steps}(d') > 0$ . So  $\neg \operatorname{leaf}(\operatorname{Shrink}(m - n'' - 1), d$ . So there must be  $p, p' \in \operatorname{ports}(d')$  such that  $p \ne p'$ , and  $\operatorname{dev}(\operatorname{peer}(p))$  and  $\operatorname{dev}(\operatorname{peer}(p'))$  in  $\operatorname{Shrink}(m - n'' - 1)$ . Fix p, p'. Now for  $x \in \{p, p'\}$ :  $\operatorname{Steps}(\operatorname{dev}(\operatorname{peer}(x))) \ge m - n'' - 1 = m - (n'' + 1) = m - n'$ . We assume without loss of generality that  $p \ne p_{2n''+1}$ .

Consider  $\pi p \mathsf{peer}(p)$ . This is a path if  $\mathsf{peer}(p) \neq p_0$ . Suppose that  $\mathsf{peer}(p) = p_0$ . Then  $p = p_1$  and  $\mathsf{dev}(p_1) = d_1$ , hence  $p_2 \dots p_n$  is a cycle, which contradicts our assumption. We conclude that  $\mathsf{peer}(p) \neq p_0$  and  $\pi p \mathsf{peer}(p)$  is a path.

Suppose that oncycle(dev(peer(p))). Then by Lemma 4.6 we have that for all  $1 \le i \le 2n'' + 1$ ,  $oncycle(dev(p_i))$ , which contradicts our assumption. So we conclude that  $\neg oncycle(dev(peer(p)))$ .

Suppose a shorter path than  $\pi p \mathsf{peer}(p)$  exists from  $\mathsf{dev}(p_0)$  to  $\mathsf{dev}(\mathsf{peer}(p))$ . This enables us to conclude that  $\mathsf{oncycle}(\mathsf{dev}(\mathsf{peer}(p_i)))$  with  $p_i \in \pi$ , which contradicts our assumptions. So we conclude that no shorter path than  $\pi p \mathsf{peer}(p)$  exists from  $\mathsf{dev}(p_0)$  to  $\mathsf{dev}(\mathsf{peer}(p))$ .

We see that the path  $\pi p p e r(p)$  meets all the requirements for the induction step.

$\boxtimes$

So there is a shortest path in the network of length m + 1. Since m > n - 1, m + 1 > n and we have a contradiction.

# 5 Verification

In this section we prove that the IEEE 1394 tree identify protocol is correct relative to our model. In Section 5.1 some properties are given which have been proved invariant for the model TIP3in [7]. Some additional properties are given, which are be proved invariant for the model TIP4, provided that the invariants for TIP3 are also invariant for TIP4. This provision is solved in the next section, Section 5.2, in which it is proved that under certain timing restrictions the behaviour of TIP4 is included in the behaviour of TIP3. The proofs in Section 5.2 allow us to conclude that the safety aspects of cycle detection and root election in TIP4 meet the IEEE 1394 requirements. In Section 5.3 we prove some liveness properties for TIP4. Finally, in Section 5.4 we discuss whether the IEEE 1394 timing constants obey the restrictions that we found in Section 5.2.

The proofs in Sections 5.1 and 5.2 use simulation techniques from [19] which are listed in Appendix A. These appendices also present a new result for using invariants in stepwise refinement, which is useful for this verification because it allows us to reuse invariants properties from [7] without extra effort. In Appendix A.2, some new sufficient conditions for feasibility can be found. These lessen the proof burden when proving that there are no time deadlocks in the model.

Throughout this section we fix a connected network  $N = \langle D, P, \text{dev}, \text{peer} \rangle$  as the parameter for TIP4. We let s,t range over states of TIP4,  $\delta$  over Time, and m over Mes.

#### 5.1 Invariants for TIP3 and TIP4

We first define the properties, of which some are taken from the PVS code used to check the proofs for [7]. All of the following properties are necessary for the proofs in Sections 5.2 and 5.3.

$$\begin{aligned} \mathbf{Definition 5.1} & I_1(d) \stackrel{\triangle}{=} \operatorname{init}[d] \rightarrow \neg \operatorname{rc}[d] \\ I_2(p) \stackrel{\triangle}{=} \operatorname{init}[\operatorname{dev}(p)] \rightarrow \operatorname{mq}[p] = \{\} \\ I_3(p) \stackrel{\triangle}{=} \operatorname{init}[\operatorname{dev}(p)] \rightarrow \operatorname{peer}(p) \not\in \operatorname{child} \\ I_4(d) \stackrel{\triangle}{=} \operatorname{init}[d] \vee \operatorname{size}(\operatorname{ports}(d) - \operatorname{child}) \leq 1 \\ I_5(p) \stackrel{\triangle}{=} \operatorname{length}(\operatorname{mq}[p]) \leq 1 \\ I_6(p) \stackrel{\triangle}{=} p \in \operatorname{child} \rightarrow \operatorname{mq}[\operatorname{peer}(p)] = \{\} \\ I_7(p) \stackrel{\triangle}{=} \operatorname{rc}[\operatorname{dev}(p)] \rightarrow \operatorname{mq}[\operatorname{peer}(p)] = \{\} \\ I_8(p) \stackrel{\triangle}{=} \operatorname{rc}[\operatorname{dev}(p)] \rightarrow \operatorname{peer}(p) \not\in \operatorname{child} \\ I_9(p) \stackrel{\triangle}{=} \vee \operatorname{init}[\operatorname{dev}(p)] \\ \vee \operatorname{head}(\operatorname{mq}[p]) = \operatorname{parent} \\ \vee \operatorname{peer}(p) \in \operatorname{child} \\ \vee \operatorname{rc}[\operatorname{dev}(\operatorname{peer}(p))] \\ \vee p \in \operatorname{child} \end{aligned}$$

$$I_{10}(p) \stackrel{\triangle}{=} \operatorname{mq}[p] \neq \{\} \rightarrow \operatorname{delay}[p] \leq \operatorname{MaxDelay} \\ I_{11}(d) \stackrel{\triangle}{=} \wedge \neg \operatorname{oncycle}(d) \wedge \operatorname{init}[d] \rightarrow \operatorname{time} \leq \operatorname{Steps}(d) * \operatorname{MaxDelay} \\ \rightarrow \forall p' \in \operatorname{ports}(d) : \\ \operatorname{head}(\operatorname{mq}[p']) = \operatorname{parent} \\ \rightarrow \operatorname{time} - \operatorname{delay}[p'] \leq \operatorname{Steps}(d) * \operatorname{MaxDelay} \end{aligned}$$

$$I_{12}(d) \stackrel{\triangle}{=} \wedge \operatorname{MinLpdtime} > \operatorname{max}(0, \operatorname{MaxHop} - 1) * \operatorname{MaxDelay} \\ \wedge \operatorname{init}[d] \\ \wedge \neg \operatorname{oncycle}(d) \\ \rightarrow \operatorname{time} < \operatorname{MinLpdtime} \end{aligned}$$

$$I_{14}(d) \stackrel{\triangle}{=} \mathtt{oncycle}(p) \land \lnot \mathtt{lpd}[d] \to \mathtt{time} \leq \mathtt{MaxLpdtime}$$

We let  $I_1 \stackrel{\triangle}{=} \bigwedge_d I_1(d), I_2 \stackrel{\triangle}{=} \bigwedge_p I_2(p)$ , et cetera.

Some of the properties in Definition 5.1 have been taken from [7], from which we also repeat the following result.

**Lemma 5.2** Properties  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $I_5$ ,  $I_6$ ,  $I_7$ ,  $I_8$ , and  $I_9$  are invariant for TIP3.

Even though the predicate oncycle has a different meaning in [7], we can assume that the proofs [7] still hold here, since the oncycle predicate is not used in the proofs.

Now we prove that under the assumption that some of the properties from Definition 5.1 hold in each reachable state for TIP4, it follows that others hold in each reachable state for TIP4 as well. In Section 5.2, the assumptions will be fulfilled by the corresponding properties for TIP3.

**Lemma 5.3** 1.  $I_{10}$  is inductive relative to  $(I_2 \wedge I_5)$  for TIP4.

- 2.  $I_{11}$  is inductive relative to  $(I_1 \wedge I_3 \wedge I_5 \wedge I_9)$  for TIP4.

- 3. For each  $s \in reachable(TIP4)$ ,  $s \models I_{11}$  implies  $s \models I_{12}$ .

- 4.  $I_{13}$  is inductive relative to  $I_3$  for TIP4.

- 5.  $I_{14}$  is inductive relative to  $I_{13}$  for TIP4.

#### Proof

- 1. Trivial.

- 2. Suppose  $\neg oncycle(d)$ .

Initially,  $s.\mathtt{time} = 0$  and  $\forall p : s.\mathtt{mq}[p] = \{\}$ . Since  $\mathtt{Steps}(d) \geq 0$ ,  $\mathtt{Steps}(d) * \mathtt{MaxDelay} \geq 0 = s.\mathtt{time}$ . Since  $\forall p \in \mathtt{ports}(d) : s.\mathtt{mq}[p] = \{\}$ , it follows that  $s \models I_{11}$ .

Suppose from  $s \xrightarrow{a} t$  and  $s \models I_1 \land I_3 \land I_5 \land I_9 \land I_{11}$ . We have to show that  $t \models I_{11}$ . Fix n such that  $n * \texttt{MaxDelay} \le s. \texttt{time} < (n+1) * \texttt{MaxDelay}$ .

We make the following case distinction.

(a) s.time > Steps(d) \* MaxDelay

By  $s \models I_{11}$  we see that  $\neg s.\mathtt{init}[d]$ . By the effect of a, we conclude that  $\neg t.\mathtt{init}[d]$ . Now we just need to show for each  $p' \in \mathtt{ports}(d)$  that if  $\mathtt{head}(t.\mathtt{mq}[p']) = \mathtt{parent}$ , then  $t.\mathtt{time}-t.\mathtt{delay}[p'] \leq \mathtt{Steps}(d)*\mathtt{MaxDelay}$ . Assume  $p' \in \mathtt{ports}(d)$  and  $\mathtt{head}(t.\mathtt{mq}[p']) = \mathtt{parent}$ . By  $\neg s.\mathtt{init}[d]$ ,  $s \models I_5$  and the precondition and effect of a,  $\mathtt{head}(s.\mathtt{mq}[p']) = \mathtt{parent}$ . Since  $s \models I_{11}$ , it follows that  $s.\mathtt{time} - s.\mathtt{delay}[p'] \leq \mathtt{Steps}(d)*\mathtt{MaxDelay}$ .

- i.  $\forall \delta > 0 : a \neq \delta$ Then by the effect of a, t.time = s.time, and by  $\neg s$ .init[d] and the precondition and effect of a, t.delay[p'] = s.delay[p']. So t.time - t.delay[p'] = s.time - s.delay[p']  $\leq$  Steps(d) \* MaxDelay and it follows that  $t \models I_{11}(d)$ .

- ii.  $a = \delta$  Then  $t.\mathtt{time} = s.\mathtt{time} + \delta$ , and  $t.\mathtt{delay}[p'] = s.\mathtt{delay}[p'] + \delta$ . So  $t.\mathtt{time} t.\mathtt{delay}[p'] = s.\mathtt{time} + \delta (s.\mathtt{delay}[p'] + \delta) = s.\mathtt{time} s.\mathtt{delay}[p'] \leq \mathtt{Steps}(d) * \mathtt{MaxDelay}$  and it follows that  $t \models I_{11}(d)$ .

- (b) s.time < Steps(d) \* MaxDelay

i.  $\neg s.init[d]$

By the effect of a,  $\neg t$ .init[d]. The remainder is equal to the proof for Step 2a.

- ii. s.init[d]

- A.  $\forall \delta > 0 : a \neq \delta$

Then by the effect of a, t.time = s.time, so t.time  $\leq$  Steps(d) \* MaxDelay, hence for each  $p' \in ports(d)$ , trivially t.time - t.delay $[p'] \leq$  Steps(d) \* MaxDelay and it follows that  $t \models I_{11}(d)$ .

- B.  $a = \delta \wedge s. \texttt{time} + \delta \leq \texttt{Steps}(d) * \texttt{MaxDelay}$ Then for each  $p' \in \texttt{ports}(d)$ , trivially  $t. \texttt{time} - t. \texttt{delay}[p'] \leq \texttt{Steps}(d) * \texttt{MaxDelay}$  and it follows that  $t \models I_{11}(d)$ .

- C.  $a = \delta \wedge s$ .time  $+ \delta > \text{Steps}(d) * \text{MaxDelay}$ The effect of a leads to a violation of property  $L_{t}$  .

The effect of a leads to a violation of property  $I_{11}$ , so we have to show that our assumption on a leads to a contradiction.

First we prove by contradiction that for each d' with  $\neg oncycle(d')$  and Steps(d') < Steps(d), it follows that  $\forall p' \in ports(d') : s.mq[p'] = \{\} \lor$ head(s.mq[p']) = ack. Suppose  $\neg oncycle(d')$ , Steps(d') < Steps(d) and head(s.mq[p']) = parent. By  $s \models I_{11}$ , we see that  $s.time - s.delay[p'] \le$ Steps(d')\*MaxDelay. Since  $t.time-t.delay[p'] = s.time+\delta-(s.delay[p']+$  $\delta$ ) = s.time - s.delay[p']  $\leq$  Steps(d') \* MaxDelay, and since s.time +  $\delta$  >  $Steps(d) * MaxDelay \ge (Steps(d') + 1) * MaxDelay$ , we get s.delay $[p'] + \delta > 0$ MaxDelay, which in contradiction with our assumption that s enables  $\delta$ . Now we prove by contradiction that for each d' with  $\neg oncycle(d')$  and  $Steps(d') \leq Steps(d)$ , it follows that  $\neg s.init[d']$ . Fix d' such that  $\neg oncycle(d')$ , s.init[d'] and there is no d'' with Steps(d'') < Steps(d') and s.init[d'']. Let  $P' = \{p' \in ports(d') | \neg oncycle(dev(peer(p'))) \land Steps(dev(peer(p'))) \le ports(d') | \neg oncycle(dev(peer(p'))) \land Steps(dev(peer(p'))) | oncycle(dev(peer(p'))) | oncycle(dev$ Steps(d') - 1. By Lemma 4.8, size(ports(d') - P')  $\leq 1$ . Fix  $p' \in P'$ and d'' = dev(peer(p')). Note that  $\text{Steps}(d'') < \text{Steps}(d') \leq \text{Steps}(d)$ . By our assumption,  $\neg s.init[d'']$ . By s.init[d'] and  $s \models I_3$ , we see  $peer(p') \notin$ s.child. By s.init[d'] and  $s \models I_1$ , we see  $\neg s.rc[d']$ . Combining all of this with our observation that  $s.mq[peer(p')] = \{\} \lor head(s.mq[peer(p')] = ack$ and  $s \models I_9$ , we get  $p' \in s$ .child. So size(ports(d')) - s.child = 1. Since

From this observation, it trivially follows that  $\neg s.\mathtt{init}[d]$  which is in contradiction with our assumption. It follows that  $a \neq \delta \lor s.\mathtt{time} + \delta \le \mathtt{Steps}(d) * \mathtt{MaxDelay}$ .

s.init[d'], s enables childrenknown(d') which is in contradiction with our

3. Let  $s \in reachable(\texttt{TIP4})$  such that  $s \models I_{11}$ . Assume  $\texttt{MinLpdtime} > \texttt{max}(0, \texttt{MaxHop} - 1) * \texttt{MaxDelay} \land s.\texttt{init}[d] \land \neg \texttt{oncycle}(d)$ . By  $s.\texttt{init}[d] \land \neg \texttt{oncycle}(d)$  and  $s \models I_{11}$ ,  $s.\texttt{time} \leq \texttt{Steps}(d) * \texttt{MaxDelay}$ . Note that for each  $n \geq 0$ ,  $\lfloor n/2 \rfloor \leq \texttt{max}(0, n-1)$ . Combining this with Lemma 4.9, we get  $\texttt{Steps}(d) \leq \texttt{max}(0, \texttt{MaxHop} - 1)$ . So  $s.\texttt{time} \leq \texttt{max}(0, \texttt{MaxHop} - 1) * \texttt{MaxDelay} < \texttt{MinLpdtime}$  and it follows that  $s \models I_{12}$ .

assumption that s enables  $\delta$ . We conclude that  $\neg s.init[d']$ .

4. Suppose oncycle(d).

Initially, s.init[d], hence  $s \models I_{13}$ .

Suppose  $s \xrightarrow{a} t$  and  $s \models I_3 \land I_{13}$ . By  $\mathtt{oncycle}(d)$  and  $s \models I_{13}$ , we see that  $s.\mathtt{init}[d]$ . If  $a \neq \mathtt{childrenknown}(d)$  then  $t.\mathtt{init}[d] = s.\mathtt{init}[d]$ , so it suffices to show that  $a \neq t$

childrenknown(d). By Lemma 4.5 and oncycle(d), there must be  $p_1, p_2 \in \mathtt{ports}(d)$  such that  $p_1 \neq p_2$  and  $\mathtt{oncycle}(\mathtt{dev}(\mathtt{peer}(p_1)))$  and  $\mathtt{oncycle}(\mathtt{dev}(\mathtt{peer}(p_2)))$ . Since  $s \models I_{13}$ , we see that  $s.\mathtt{init}[\mathtt{dev}(\mathtt{peer}(p_1))]$  and  $s.\mathtt{init}[\mathtt{dev}(\mathtt{peer}(p_2))]$ . Since  $s \models I_3$ , we see that  $p_1 \notin s.\mathtt{child}$  and  $p_2 \notin s.\mathtt{child}$ . Since  $p_1 \neq p_2$ , we see that  $\mathtt{size}(\mathtt{ports}(d) - s.\mathtt{child} \geq 2$ , hence s does not enable  $\mathtt{childrenknown}(d)$ .

5. Trivial.

$\boxtimes$

Note that by Items 2 and 3 it follows that  $I_{12}$  is inductive relative to  $(I_1 \wedge I_3 \wedge I_5 \wedge I_9 \wedge I_{11})$  for TIP4.

### 5.2 TIP4 implements TIP3

We use the properties established in Section 5.1 to obtain that TIP4 implements TIP3. As an implementation relation we take inclusion of admissible timed traces. From Section 5.1, it follows that the behaviour of TIP4 meets these properties only when the parameters obey the following relation: MinLpdtime > max(0, MaxHop - 1) \* MaxDelay. Therefore, we assume throughout this section that this relation holds.

In order to obtain the implementation relation, we construct a function that is to be proved a weak timed refinement from TIP4 to TIP3. Given the complicated relations between the invariants for TIP3 and the properties for TIP4, we have been forced to either prove the properties for TIP4 that depend on invariants for TIP3 anew, or to prove the invariance of the properties for TIP4and the weak refinement in one proof, or to come up with a more elegant solution. The latter approach has given rise to some new sufficient conditions, which are presented in Appendix A.

To avoid confusion, all state variables from TIP3 are subscripted with 3, and all state variables from TIP4 are subscripted with 4. Since the action signatures are equal, we do not use these subscript on the action names.

**Definition 5.4** The function **ref** from states of TIP4 to states of TIP3 is defined to be the identity function on state variables with the same name.

**Lemma 5.5** Let  $s \in states(\texttt{TIP3})$ . For all  $I \in \{I_1, I_2, I_3, I_4, I_5, I_6, I_7, I_8, I_9\}$ ,  $\texttt{ref}(s) \models I$  implies  $s \models I$ .

**Lemma 5.6** 1.  $s \in Start(TIP4)$  implies  $ref(s) \in Start(TIP3)$ .

2.  $s \xrightarrow[]{a}_{\text{TIP4}} t$ ,  $s \models I_{10} \land I_{11} \land I_{12} \land I_{13} \land I_{14}$  and  $\text{ref}(s) \models I_1 \land I_2 \land I_3 \land I_4 \land I_5 \land I_6 \land I_7 \land I_8 \land I_9$  implies  $\text{ref}(s) \xrightarrow[]{a}_{\text{TIP3}} \text{ref}(t)$ .

#### **Proof**

1. Suppose  $s \in Start(TIP4)$ .

Since the initial requirements are the same for every state variable in TIP3 as for the state variable with the same name in TIP4, and the state variables with the same name have the same value in s and in ref(s),  $ref(s) \in Start(TIP3)$  follows from  $s \in Start(TIP4)$ .

2. Suppose  $s \xrightarrow[]{a}_{\text{TIP4}} t \ s \models I_{10} \land I_{11} \land I_{12} \land I_{13} \land I_{14} \text{ and } \text{ref}(s) \models I_1 \land I_2 \land I_3 \land I_4 \land I_5 \land I_6 \land I_7 \land I_8 \land I_9.$  $s \in reachable(\text{TIP4}) \text{ and } \text{ref}(s) \in reachable(\text{TIP3}).$

Since for each a, the effect in TIP3 is equal to the effect in TIP4 on all state variables from TIP3, it follows that whenever  $\operatorname{ref}(s) \xrightarrow{a}_{\operatorname{TIP3}} t'$ , then  $t' = \operatorname{ref}(t)$ .

If  $a \notin \bigcup_d \mathtt{loopdetect}(d)$ , then we see that the precondition of a in TIP4 trivially implies the precondition of a in TIP3, hence if  $s \xrightarrow[]{a}_{\mathsf{TIP4}}$ , then  $\mathtt{ref}(s) \xrightarrow[]{a}_{\mathsf{TIP3}}$ . So we just need to show that if  $a = \mathtt{loopdetect}(a)$ , then  $\mathtt{ref}(s) \xrightarrow[]{a}_{\mathsf{TIP3}}$ .

Suppose  $a = \mathtt{loopdetect}(a)$ . By precondition of a in TIP4,  $\neg s.\mathtt{lpd_4}[d]$  and  $s.\mathtt{time_4} \ge \mathtt{MinLpdtime}$ . From  $\neg s.\mathtt{lpd_4}[d]$  we see  $\neg \mathtt{ref}(s).\mathtt{lpd_3}[d]$ . By  $s.\mathtt{time_4} = \mathtt{lpdtime_4}[d]$  and  $s \models I_{12}$  we see that either  $\neg s.\mathtt{init_4}[d]$  or  $\mathtt{oncycle}(d)$ . By precondition of a in TIP4 we see that  $s.\mathtt{init_4}[d]$ , and we conclude that  $\mathtt{oncycle}(d)$ . Hence  $\mathtt{ref}(s)$  enables a.

Corollary 5.7  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_4$ ,  $I_5$ ,  $I_6$ ,  $I_7$ ,  $I_8$ ,  $I_9$ ,  $I_{10}$ ,  $I_{11}$ ,  $I_{12}$ ,  $I_{13}$  and  $I_{14}$  are invariant for TIP4.

**Proof** By Lemmas 5.2, 5.3, 5.5 and 5.6 we can use Lemma A.2.

**Corollary 5.8** The function ref is a weak timed refinement from TIP4 to TIP3 with respect to  $(I_{10} \wedge I_{11} \wedge I_{12} \wedge I_{13} \wedge I_{14})$  and  $(I_1 \wedge I_2 \wedge I_3 \wedge I_4 \wedge I_5 \wedge I_6 \wedge I_7 \wedge I_8 \wedge I_9)$

**Proof** By Lemmas 5.2, 5.3, 5.5 and 5.6 we can use Lemma A.2.

⊠

The implementation relation now follows easily.

**Theorem 5.9** t-traces(TIP4)  $\subseteq t$ -traces(TIP3).

**Proof** Combine Corollary 5.8 with Theorem 6.14 from [19].

### 5.3 Liveness results for TIP4

In this section we show some liveness results for model TIP4. As in Section 5.2, we assume that the parameters of TIP4 meet the following relation: MinLpdtime > max(0, MaxHop-1)\*MaxDelay.

The liveness results are the following. We first show that TIP4 has no time deadlocks. For this, some new sufficient conditions are used, which are presented in Appendix A.2. Then we prove that when a cycle is present, it will be detected, and that otherwise a root will be elected. Notice that we cannot use results from TIP3, since notions as quiescence and fairness are not present at the timed level.

First we need to define a measure on reachable states, to indicate the number of discrete actions that must be performed before passing of time will be enabled again.

$\boxtimes$

$\boxtimes$

$\boxtimes$

**Definition 5.10** The function Measure gives a pair for each state s from TIP4, as follows:

```

\begin{split} \text{Measure}(s) &= \langle I, C + R + M + L \rangle \\ where \\ I &= \text{size}(\{d|s.\text{init}[d]\}) \\ C &= \text{size}(P - s.\text{child}) \\ R &= \text{size}(\{d|\neg s.\text{root}[d]\}) \\ M &= \text{size}(\{p|s.\text{mq}[p] \neq \{\}\}) \\ L &= \text{size}(\{d|\neg s.\text{lpd}[d]\}) \end{split}

```

The ordering  $\prec$  is the lexicographic ordering on pairs of naturals, based on the ordering < on naturals.

Since < is well-founded,  $\prec$  is also well-founded.

Now we prove the properties that we need for deadlock freedom, namely that when no discrete action is enabled, then the passage of time is enabled, and that at every moment in time at most a finite amount of discrete activity can occur.

**Lemma 5.11** For each  $s \in reachable(TIP4)$  the following holds:

- 1. s enables an action from acts(TIP4).

- 2. If  $s \xrightarrow{a} t$  and  $\forall \delta > 0 : a \neq \delta$ , then  $\texttt{Measure}(t) \prec \texttt{Measure}(s)$  otherwise Measure(t) = Measure(s).

#### Proof

1. It suffices to show that if s does not enable a for all  $a \in acts(Tipvier) - \bigcup_{\delta>0} \{\delta\}$ , then s enables  $\delta$  for some  $\delta > 0$ , which we prove by contradiction.

Suppose that for all  $a \in acts(\texttt{TIP4})$ , s does not enable a. Apparently s does not enable any  $\delta > 0$ , so either s.time = MaxLpdtime and  $\exists d : s.\texttt{init}[d] \land \neg s.\texttt{lpd}[d]$ , or  $\exists p : s.\texttt{mq}[p] \neq \{\} \land s.\texttt{delay}([p]) \geq \texttt{MaxDelay}$ .

Suppose s.time = MaxLpdtime, s.init[d] and  $\neg s.lpd[d]$ . Then s enables loopdetect(d) and we have a contradiction.

Suppose  $s.mq[p] \neq \{\}$  and  $s.delay[p] \geq MaxDelay$ . Let head(s.mq[p]) = m. Since  $MaxDelay \geq MinDelay$ ,  $s.delay[p] \geq MinDelay$ . Using Invariant  $I_2$ , we get  $\neg s.init[dev(p)]$ , and using Invariant  $I_6$  we get  $peer(p) \not\in s.child$ . Suppose  $p \in s.child$ . Using Invariant  $I_3$  we get  $\neg s.init[dev(peer(p))]$ . Then s enables receivemes(dev(peer(p)), peer(p), m) and we have a contradiction. So  $p \not\in s.child$ . Using Invariant  $I_7$ , we see that  $\neg s.rc[dev(peer(p))]$ . Combining all of this with  $I_9$  we get m = parent. Suppose s.init[dev(peer(p))]. Then s enables addchild(dev(peer(p)), peer(p)) and we have a contradiction. So  $\neg s.init[dev(peer(p))]$ . Then s enables receivemes(dev(peer(p)), peer(p), pe

- 2. Let Measure(s) =  $\langle I_s, C_s + R_s + M_s + L_s \rangle$  and Measure(t) =  $\langle I_t, C_t + R_t + M_t + L_t \rangle$ .

- (a)  $a = \mathtt{childrenknown}(d)$ By precondition of a,  $\neg s.\mathtt{init}[d]$  and by effect of a,  $t.\mathtt{init}[d]$ . So  $I_t < I_s$ . We conclude that  $\mathtt{Measure}(t) \prec \mathtt{Measure}(s)$ .

(b)  $a = \operatorname{addchild}(d,p)$ By effect of a,  $t.\operatorname{init} = s.\operatorname{init}$ ,  $t.\operatorname{root} = s.\operatorname{root}$  and  $t.\operatorname{lpd} = s.\operatorname{lpd}$ , hence  $I_t = I_s$ ,  $R_t = R_s$  and  $L_t = L_s$ . By precondition of a,  $\operatorname{head}(s.\operatorname{mq[peer}(p)] = \operatorname{parent}$ . Combining this with Invariant  $I_5$ , we get  $s.\operatorname{mq[peer}(p)] = \{\}$   $\vdash$  parent. By the effect of a,  $t.\operatorname{mq[peer}(p)] = \operatorname{tail}(s.\operatorname{mq[peer}(p)]) = \{\}$ , so  $M_t = M_s - \{\operatorname{peer}(p)\}$ , hence  $M_t < M_s$ . Combining  $\operatorname{head}(s.\operatorname{mq[peer}(p)] = \operatorname{parent}$  with Invariant  $I_6$  we get  $p \not\in s.\operatorname{child}$ . By effect of a,  $t.\operatorname{child} = s.\operatorname{child} \cup \{p\}$ . So  $C_t < C_s$ . By effect of a We conclude that  $\operatorname{Measure}(t) \prec \operatorname{Measure}(s)$ .

- (c)  $a = \mathtt{receivemes}(d, p, m)$ By effect of a,  $t.\mathtt{init} = s.\mathtt{init}$ ,  $t.\mathtt{child} = s.\mathtt{child}$ ,  $t.\mathtt{root} = s.\mathtt{root}$  and  $t.\mathtt{lpd} = s.\mathtt{lpd}$ , hence  $I_t = I_s$ ,  $C_t = C_s$ ,  $R_t = R_s$  and  $L_t = L_s$ . By precondition of a, head $(s.\mathtt{mq}[\mathtt{peer}(p)] = m$ . Combining this with Invariant  $I_5$ , we get  $s.\mathtt{mq}[\mathtt{peer}(p)] = \{\} \vdash m$ . By the effect of a,  $t.\mathtt{mq}[\mathtt{peer}(p)] = \mathtt{tail}(s.\mathtt{mq}[\mathtt{peer}(p)]) = \{\}$ , so  $M_t = M_s - \{\mathtt{peer}(p)\}$ , hence  $M_t < M_s$ . We conclude that Measure $(t) \prec \mathtt{Measure}(s)$ .

- (d)  $a = \mathtt{solverootcontent}(d, p)$ By effect of  $a, t.\mathtt{init} = s.\mathtt{init}, t.\mathtt{root} = s.\mathtt{root}, t.\mathtt{mq} = s.\mathtt{mq} \text{ and } t.\mathtt{lpd} = s.\mathtt{lpd}, \text{ hence } I_t = I_s, \ R_t = R_s, \ M_t = M_s \text{ and } L_t = L_s.$  By precondition of  $a, s.\mathtt{rc}[\mathtt{dev}(\mathtt{peer}(p))].$  Combining this with Invariant  $I_8$  we get  $p \not\in s.\mathtt{child}$ . By effect of  $a, t.\mathtt{child} = s.\mathtt{child} \cup \{p\}.$  So  $C_t < C_s$ . We conclude that  $\mathtt{Measure}(t) \prec \mathtt{Measure}(s)$ .

- (e)  $a = \mathtt{root}(d)$ By effect of a,  $s.\mathtt{init} = t.\mathtt{init}$ ,  $s.\mathtt{child} = t.\mathtt{child}$ ,  $t.\mathtt{mq} = s.\mathtt{mq}$  and  $t.\mathtt{lpd} = s.\mathtt{lpd}$ , hence  $I_t = I_s$ ,  $C_t = C_s$ ,  $M_t = M_s$  and  $L_t = L_s$ . By precondition of a,  $\neg s.\mathtt{root}[d]$ , and by effect of a,  $t.\mathtt{root}[d]$ . So  $R_t < R_s$ . We conclude that  $\mathtt{Measure}(t) \prec \mathtt{Measure}(s)$ .

- (f)  $a = \mathtt{loopdetect}(d)$ By effect of a,  $s.\mathtt{init} = t.\mathtt{init}$ ,  $s.\mathtt{child} = t.\mathtt{child}$ ,  $s.\mathtt{root} = t.\mathtt{root}$  and  $s.\mathtt{mq} = t.\mathtt{mq}$ , hence  $I_t = I_s$ ,  $C_t = C_s$ ,  $R_t = R_s$  and  $M_t = M_s$ . By precondition of a,  $\neg s.\mathtt{lpd}[d]$ , and by effect of a,  $t.\mathtt{lpd}[d]$ . So  $L_t < L_s$ . We conclude that  $\mathtt{Measure}(t) \prec \mathtt{Measure}(s)$ .

- (g)  $a = \delta$ By effect of a, s.init = t.init, s.child = t.child, s.root = t.root, s.mq = t.mq and t.lpd = s.lpd. Hence  $I_t = I_s$ ,  $C_t = C_s$ ,  $R_t = R_s$ ,  $M_t = M_s$  and  $L_t = L_s$ , and we conclude that Measure(t) = Measure(s).

$\boxtimes$

Now we show that TIP4 cannot get into a time deadlock by its own discrete activity. A timed I/O automaton that has this property is called *feasible*.

### Theorem 5.12 TIP4 is feasible.

**Proof** It can easily be seen that TIP4 fulfills the requirements for Lemma A.3. This lemma fulfills one of the requirements in Theorem A.4. The other requirement is fulfilled by the Measure function and the result in Proposition 5.11. It follows from Theorem A.4 that TIP4 is feasible.

⊠

We now show that whenever there is a cycle in the network, it is detected by the protocol.

**Theorem 5.13** Let  $\alpha$  be an admissible execution of TIP4. If  $\operatorname{oncycle}(d)$  then  $\alpha$  contains an occurrence of  $\operatorname{lpd}(d)$ .

**Proof** Since time proceeds in  $\alpha$  without bound, and since initially  $s.\mathtt{lpd}[d]$  is false and since  $s.\mathtt{lpd}[d]$  can only be made true by an occurrence of  $\mathtt{lpd}(d)$ , it suffices to show that for each reachable state s in TIP4, if  $s.\mathtt{time} > \mathtt{MaxLpdtime}$ , then  $s.\mathtt{lpd}[d]$ . This follows easily from Invariant  $I_{14}$ .

Unfortunately, it is not possible to prove that if there is no cycle in the network, then within finite time a root will be elected. This is due to the unknown duration of the root contention solving sub-protocol. The following theorem shows that if no root contention occurs, then indeed a root is elected in finite time.

**Theorem 5.14** Let  $\alpha = s_0 a_1 s_1 \dots$  be an admissible execution of TIP4.

If  $\forall d : \neg \mathtt{oncycle}(d)$  and  $\forall i, d : \neg s_i \cdot \mathtt{rc}[d]$ , then  $\exists d$  such that  $\alpha$  contains an occurrence of  $\mathtt{root}(d)$ .

**Proof** Assume  $\forall d : \neg \mathsf{oncycle}(d)$ . We observe the following:

- 1. Time proceeds in  $\alpha$  without bound.

- 2. In each reachable state s in TIP4 the following holds. For all d: if s is an initial state then  $\neg s.\mathtt{root}[d]$ , and if  $s.\mathtt{root}[d]$ , then each execution leading to s must contain an occurrence of  $\mathtt{root}(d)$ .

- 3. If there is a state s in  $\alpha$  and a d such that  $ports(d) s.child = {}$ , then  $\alpha$  contains an occurrence of root(d).