# Formal Verification of Distributed Systems

Jan Pang

# Formal Verification of Distributed Systems

Jun Pang

August, 2004

© Jun Pang, Amsterdam 2004 Printed by Ponsen & Looijen B.V. ISBN 90-6464-865-4

This research has been supported by PROGRESS, the embedded systems research program of the Dutch organisation for Scientific Research (NWO), the Dutch Ministry of Economic Affairs and the Technology Foundation (STW), within the scope of the project CES.5008 "Improving the Quality of Embedded Systems using Formal Design and Systematic Testing". It has been carried out under the auspices of the Institute for Programming Research and Algorithmics (IPA), at the Centrum voor Wiskunde en Informatica (CWI) in Amsterdam.

# Contents

|   | Pre                              | eface                                                                                                                                                                                                                              | 1                                |

|---|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1 | Int.<br>1.1<br>1.2<br>1.3<br>1.4 | The Title                                                                                                                                                                                                                          | 3<br>5<br>6<br>9                 |

| 2 | 2.1<br>2.2<br>2.3<br>2.4<br>2.5  | Eliminaries $\mu$ CRL                                                                                                                                                                                                              | 11<br>13<br>14<br>15<br>17       |

| Ι | $\mathbf{T}$                     | neorem Proving                                                                                                                                                                                                                     | 19                               |

| 3 | Cor 3.1 3.2                      | nes and Foci: A Mechanical Proof Framework Introduction                                                                                                                                                                            | 21<br>21<br>24<br>25             |

|   | 3.3                              | 3.2.2 Proof rules for reachability A Mechanical Proof Framework 3.3.1 LTSs and branching bisimulation 3.3.2 Representing LPEs and invariants 3.3.3 Formalizing the cones and foci method 3.3.4 The symbolic reachability criterion | 26<br>27<br>28<br>30<br>31<br>33 |

|   | 3.4                              | Application to the CABP                                                                                                                                                                                                            | 34<br>35<br>36<br>39<br>44<br>48 |

ii Contents

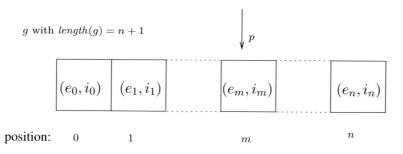

| 4  | Veri                   | ifying a Sliding Window Protocol in $\mu CRL$                  | <b>51</b> |

|----|------------------------|----------------------------------------------------------------|-----------|

|    | 4.1                    | Introduction                                                   | 51        |

|    | 4.2                    | Related Work                                                   | 53        |

|    | 4.3                    | Proof Techniques                                               | 54        |

|    | 4.4                    | Data Types                                                     | 55        |

|    |                        | 4.4.1 Booleans                                                 | 55        |

|    |                        | 4.4.2 If-then-else and equality                                | 55        |

|    |                        | 4.4.3 Natural numbers                                          | 56        |

|    |                        | 4.4.4 Modulo arithmetic                                        | 56        |

|    |                        | 4.4.5 Buffers                                                  | 56        |

|    |                        | 4.4.6 Mediums                                                  | 58        |

|    |                        | 4.4.7 Lists                                                    | 59        |

|    | 4.5                    | Sliding Window Protocol                                        | 59        |

|    |                        | 4.5.1 Specification of a sliding window protocol               | 59        |

|    |                        | 4.5.2 External behavior                                        | 62        |

|    | 4.6                    | Transformations of the Specification                           | 62        |

|    |                        | 4.6.1 Linearization                                            | 62        |

|    |                        | 4.6.2 Eliminating arguments of communication actions           | 64        |

|    |                        | 4.6.3 Getting rid of modulo arithmetic                         | 64        |

|    | 4.7                    | Properties of Data                                             | 65        |

|    |                        | 4.7.1 Basic properties                                         | 65        |

|    |                        | 4.7.2 Invariants                                               | 79        |

|    | 4.8                    | Correctness of $N_{mod}$                                       | 92        |

|    |                        | 4.8.1 Equality of $\mathbf{N}_{mod}$ and $\mathbf{N}_{nonmod}$ | 92        |

|    |                        | 4.8.2 Correctness of $N_{nonmod}$                              | 96        |

|    |                        | 4.8.3 Correctness of the sliding window protocol               | 102       |

|    | 4.9                    | Conclusions                                                    | 102       |

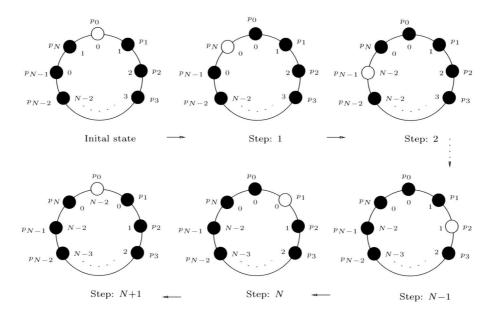

| 5  | ΑN                     | Note on $K$ -state Self-Stabilization in a Ring with $K = N$   | 103       |

|    | 5.1                    | Introduction                                                   | 103       |

|    | 5.2                    | Proof of Self-Stabilization                                    | 105       |

|    | 5.3                    | Mechanical Verification in PVS                                 | 107       |

|    | 5.4                    | K = N is Sharp                                                 |           |

|    | 5.5                    | Conclusions                                                    | 110       |

|    |                        |                                                                | 111       |

| IJ | l N                    | Model Checking                                                 | 111       |

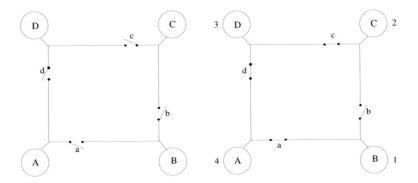

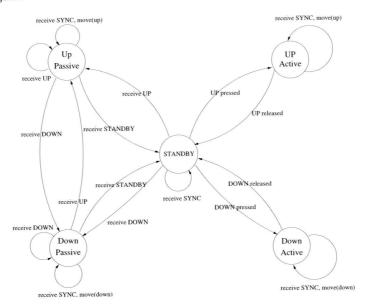

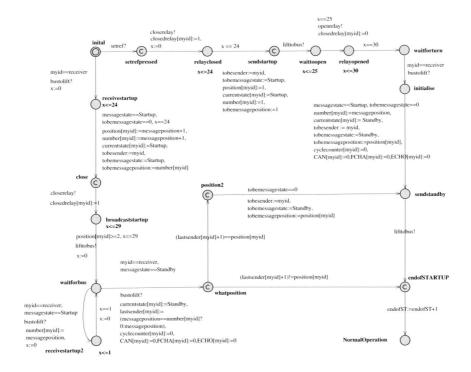

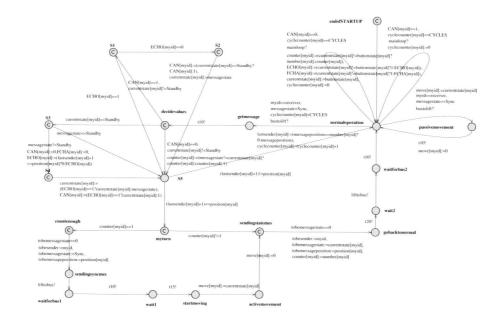

| 6  | $\mathbf{A}\mathbf{n}$ | alysis of a Distributed System for Lifting Trucks              | 113       |

|    | 6.1                    | Introduction                                                   | 113       |

|    | 6.2                    | Description of the Lift System                                 |           |

|    |                        | 6.2.1 Layout of the lift system                                |           |

|    | 505 100                | 6.2.2 Control of lift movement                                 |           |

|    | 6.3                    | Requirements                                                   |           |

|    | 6.4                    | $\mu$ CRL Model of the Original Design                         |           |

|    |                        | 6.4.1 Data types                                               | 120       |

Contents

|   |      | 6.4.2 Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 6.5  | Analysis the Original Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |      | 6.5.1 Problem 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 6.5.2 Problem 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 6.5.3 Problem 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 6.5.4 Problem 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 6.6  | Verification with CADP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |      | 6.6.1 Expressing the requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |      | 6.6.2 Verifying the modified specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.7  | UPPAAL Model of the Redesign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |      | 6.7.1 Transforming the $\mu$ CRL model 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |      | 6.7.2 Adding the solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |      | 6.7.3 Adding timing information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 6.8  | Analysis of the Redesign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |      | 6.8.1 Expressing the requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |      | 6.8.2 Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 6.9  | A New Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 6.10 | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

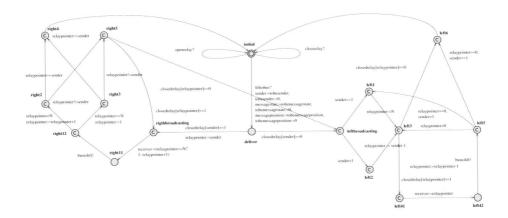

| 7 |      | del Checking a Cache Coherence Protocol for Jackal 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 7.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 7.2  | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

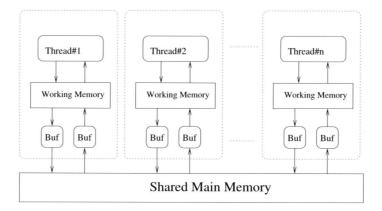

|   | 7.3  | Java Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

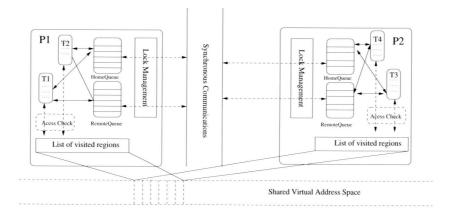

|   | 7.4  | Jackal DSM System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |      | 7.4.1 Address space management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |      | 7.4.2 Access check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |      | 7.4.3 Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |      | 7.4.4 Automatic home node migration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |      | 7.4.5 Other features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 7.5  | Specification and Analysis in $\mu$ CRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |      | 7.5.1 Specification of the protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |      | 7.5.2 Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |      | 7.5.3 Validation of the requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |